Question: Problem 2: Assume that each pipeline register and the program counter have a delay of 20ps. Times taken by other major hardware units in a

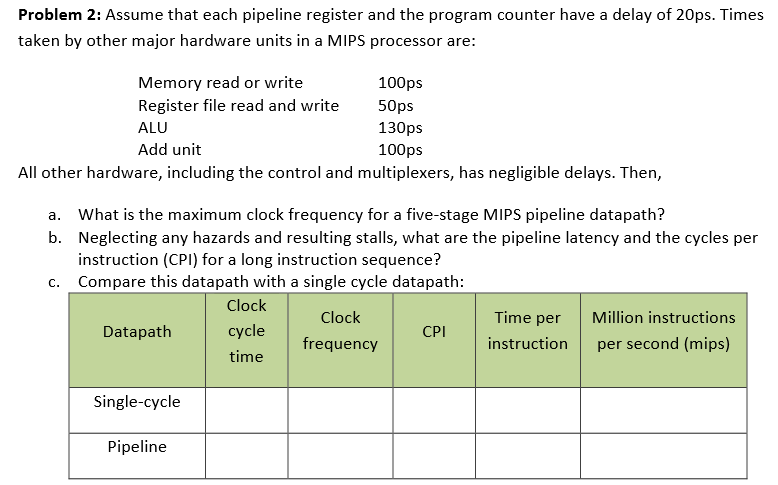

Problem 2: Assume that each pipeline register and the program counter have a delay of 20ps. Times taken by other major hardware units in a MIPS processor are Memory read or write Register file read and write ALU Add unit 100ps 50ps 130ps 100ps All other hardware, including the control and multiplexers, has negligible delays. Then, What is the maximum clock frequency for a five-stage MIPS pipeline datapath? Neglecting any hazards and resulting stalls, what are the pipeline latency and the cycles per instruction (CPI) for a long instruction sequence? a. b. c. Compare this datapath with a single cycle datapath: Clock cycle time Time per Million instructions instruction per second (mips) Clock Datapath CPI frequency Single-cycle Pipeline

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts