Question: Problem # 2 The following is a typical assembly language instruction from the MIPS instruction set architecture. ADD $s 3 , $t 2 , $s

Problem #

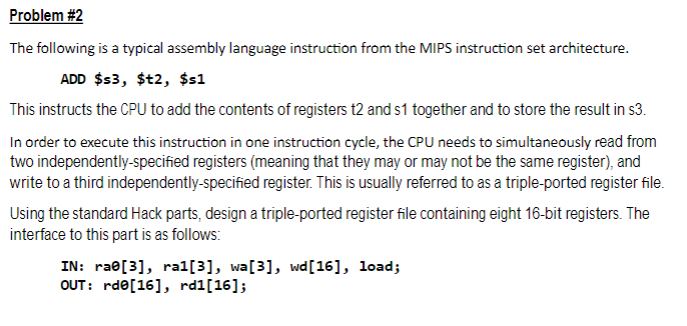

The following is a typical assembly language instruction from the MIPS instruction set architecture.

ADD $s $t $s

This instructs the CPU to add the contents of registers t and s together and to store the result in s

In order to execute this instruction in one instruction cycle, the CPU needs to simultaneously read from

two independentlyspecified registers meaning that they may or may not be the same register and

write to a third independentlyspecified register. This is usually referred to as a tripleported register file.

Using the standard Hack parts, design a tripleported register file containing eight bit registers. The

interface to this part is as follows:

: rae load;

OUT: rde;

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock