Question: Problem #3: Retiming Consider the following combinational logie circuit below. Individual functions are marked with their delay itn microsecond and cannot be further divided. Solid

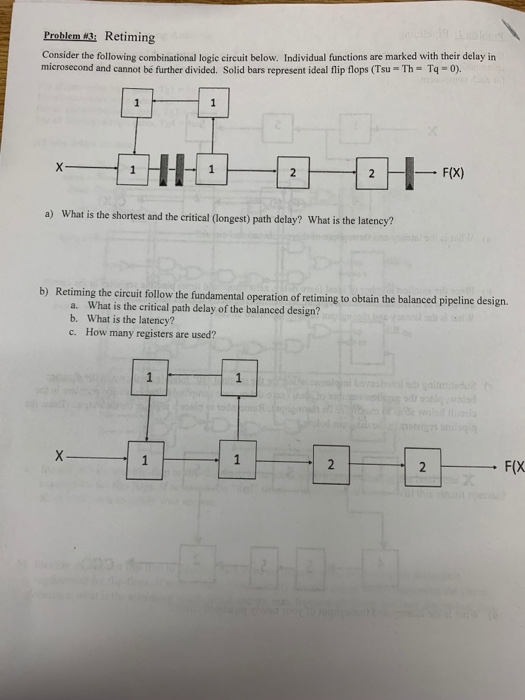

Problem #3: Retiming Consider the following combinational logie circuit below. Individual functions are marked with their delay itn microsecond and cannot be further divided. Solid bars represent ideal flip flops (Tsu Th Tq -0) a) What is the shortest and the critical (longest) path delay? What is the latency? b) Retiming the circuit follow the fundamental operation of retiming to obtain the balanced pipeline design. a. What is the critical path delay of the balanced design? b. What is the latency? c. How many registers are used? F(X Problem #3: Retiming Consider the following combinational logie circuit below. Individual functions are marked with their delay itn microsecond and cannot be further divided. Solid bars represent ideal flip flops (Tsu Th Tq -0) a) What is the shortest and the critical (longest) path delay? What is the latency? b) Retiming the circuit follow the fundamental operation of retiming to obtain the balanced pipeline design. a. What is the critical path delay of the balanced design? b. What is the latency? c. How many registers are used? F(X

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts