Question: Problem 5 (10pts). Let's simplify the MIPS instruction set architecture a little by removing the original lw and su instructions and replacdng them with ones

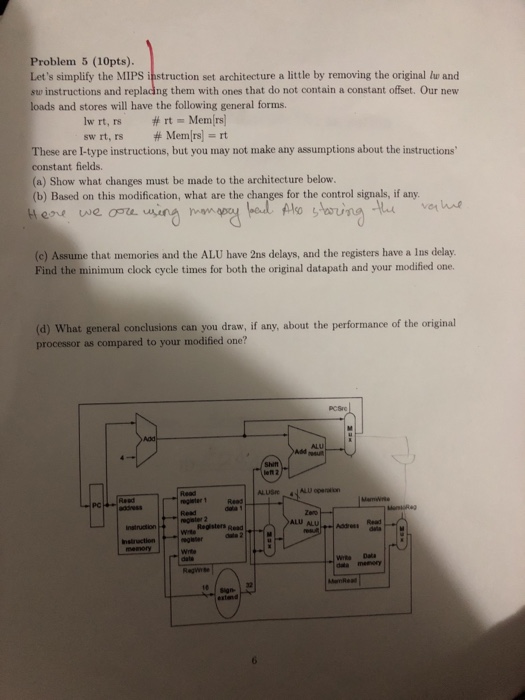

Problem 5 (10pts). Let's simplify the MIPS instruction set architecture a little by removing the original lw and su instructions and replacdng them with ones that do not contain a constant offset. Our new loads and stores will have the following general forms. 1w rt, rs swrt, rs #rt-Mem[rs] #Memlrs]-rt These are I-type instructions, but you may not make any assumptions about the instructions constant fields. (a) Show what changes must be made to the architecture below (b) Based on this modification, what are the changes for the control signals, if any (c) Assume that memories and the ALU have 2ns delays, and the registers have a Ins delay Find the minimum clock cycle times for both the original datapath and your modified one (d) What general conclusions can you draw, if any, about the performance of the original processor as compared to your modified one? let 2 egister 1 Re Zero instructionH Registers Read Wrte Dat sign

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts