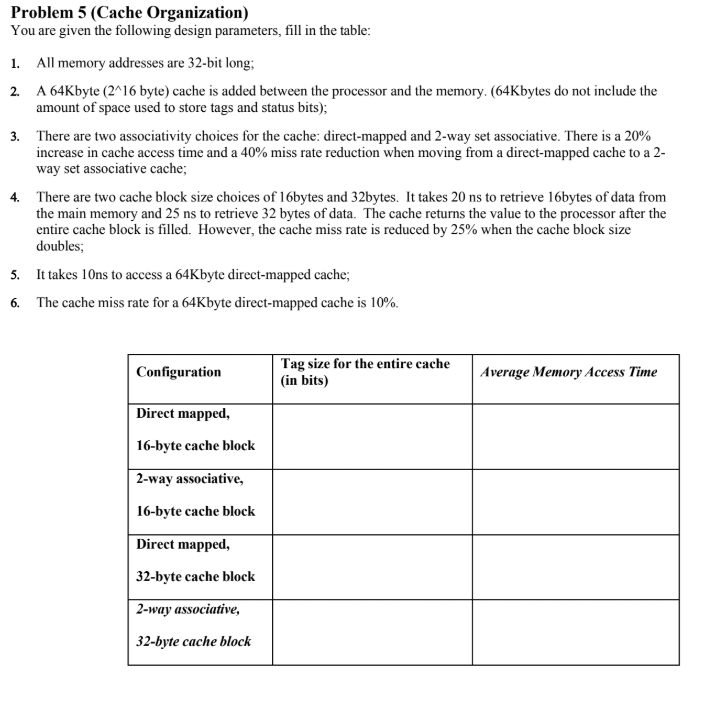

Question: Problem 5 ( Cache Organization ) You are given the following design parameters, fill in the table: 1 . All memory addresses are 3 2

Problem Cache Organization

You are given the following design parameters, fill in the table:

All memory addresses are bit long;

A Kbyte wedge byte cache is added between the processor and the memory. Kbytes do not include the amount of space used to store tags and status bits;

There are two associativity choices for the cache: directmapped and way set associative. There is a increase in cache access time and a miss rate reduction when moving from a directmapped cache to a way set associative cache;

There are two cache block size choices of bytes and bytes. It takes ns to retrieve bytes of data from the main memory and ns to retrieve bytes of data. The cache returns the value to the processor after the entire cache block is filled. However, the cache miss rate is reduced by when the cache block size doubles;

It takes ns to access a Kbyte directmapped cache;

The cache miss rate for a Kbyte directmapped cache is

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock