Question: PROBLEM 5: CACHE (20 POINTS) Assuming a 32-bit address size in the following questions: A. (5 points) Diagram out the bits used for tag, index

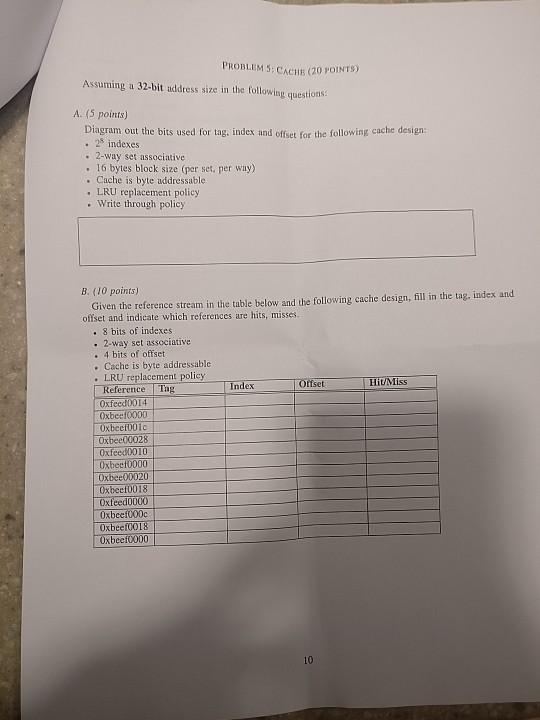

PROBLEM 5: CACHE (20 POINTS) Assuming a 32-bit address size in the following questions: A. (5 points) Diagram out the bits used for tag, index and offset for the following cache design 2 indexes 2-way set associative 16 bytes block size (per set, per way) . Cache is byte addressable . LRU replacement policy Write through policy B. (10 points Given the reference stream in the table below and the following cache design, fill in the tag, index and . 8 bits of indexes . 4 bits of offset offset and indicate which references are hits, misses. 2-way set associative . Cache is byte addressable LRU replacement policy Offset Reference Thg Oxfeed0O14 Oxbee Oxbee00028 Oxbee00020 Oxbee 10

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts