Question: Problem 5 : Consider a 6 - stage MIPS pipelined processor with the following stages: IF , ID , EX , MEM, BR , WB

Problem :

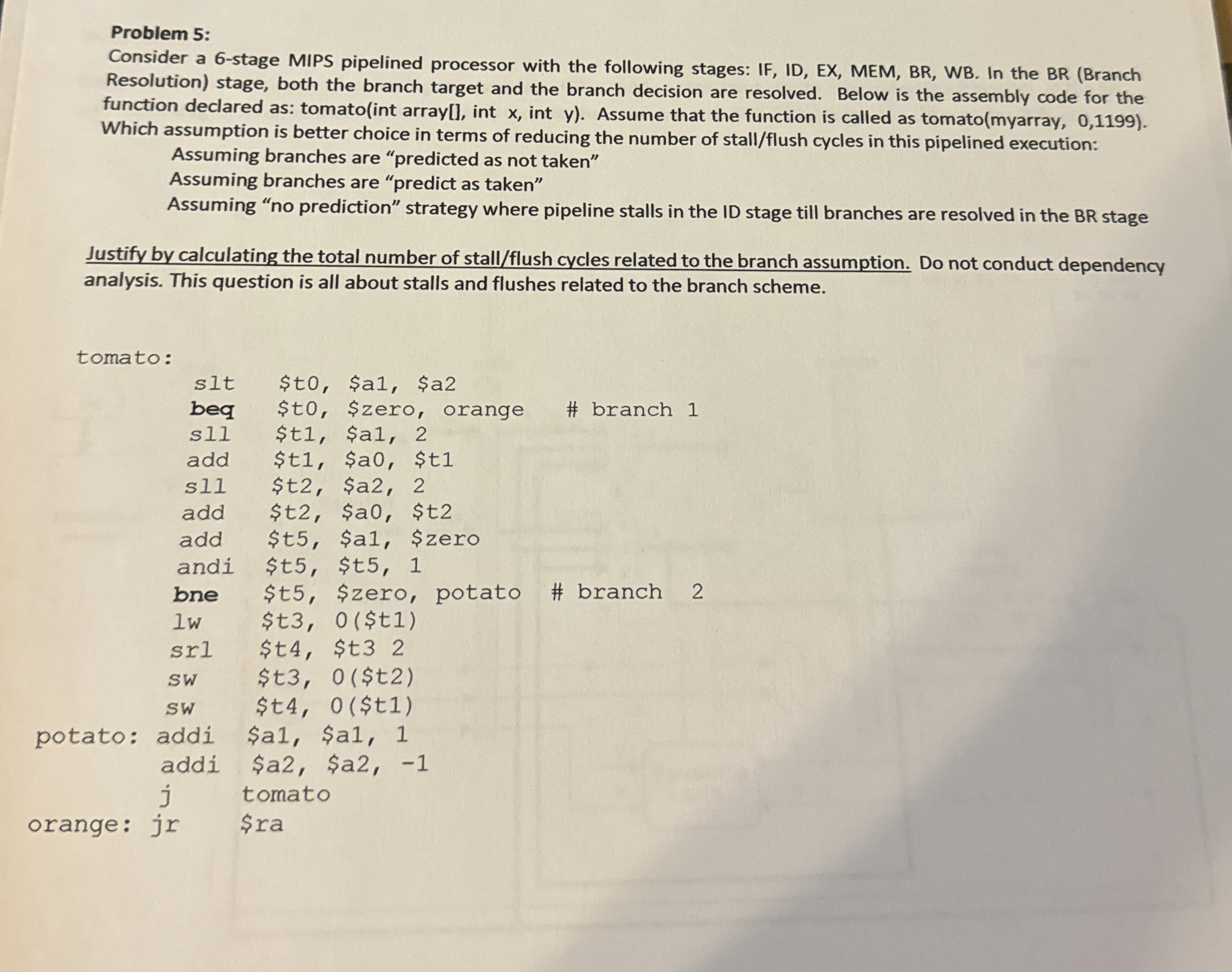

Consider a stage MIPS pipelined processor with the following stages: IF ID EX MEM, BR WB In the BR Branch Resolution stage, both the branch target and the branch decision are resolved. Below is the assembly code for the function declared as: tomatoint array int int Assume that the function is called as tomatomyarray Which assumption is better choice in terms of reducing the number of stallflush cycles in this pipelined execution:

Assuming branches are "predicted as not taken"

Assuming branches are "predict as taken"

Assuming no prediction" strategy where pipeline stalls in the ID stage till branches are resolved in the BR stage

Justify by calculating the total number of stallflush cycles related to the branch assumption. Do not conduct dependency analysis. This question is all about stalls and flushes related to the branch scheme.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock