Question: provide VHDL code, The Testbench and the waveform Problem 1: (30 pts) Design a 16-bit Arithmetic Unit which consists of one 16-bit adder, 16-bit subtractor,

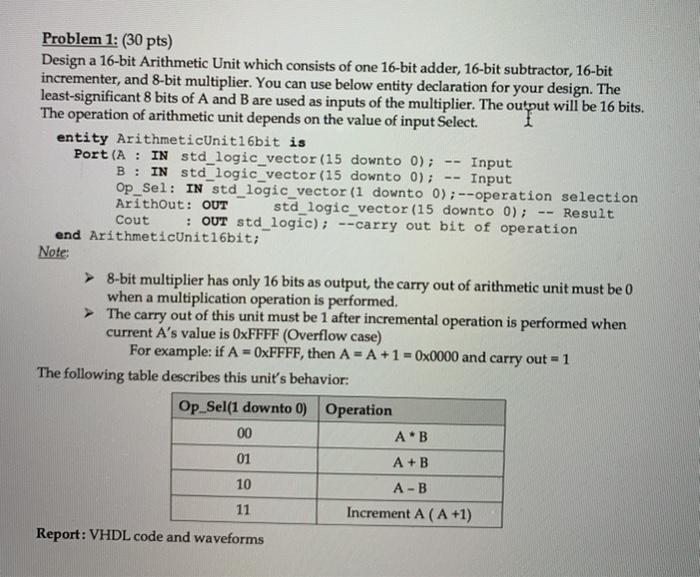

Problem 1: (30 pts) Design a 16-bit Arithmetic Unit which consists of one 16-bit adder, 16-bit subtractor, 16-bit incrementer, and 8-bit multiplier. You can use below entity declaration for your design. The least-significant 8 bits of A and B are used as inputs of the multiplier. The output will be 16 bits. The operation of arithmetic unit depends on the value of input Select. entity ArithmeticUnit16bit is Port (A : IN std_logic_vector (15 downto 0); -- Input B: IN std logic vector (15 downto 0); Input Op_Sel: IN std_logic_vector (1 downto 0); --operation selection Arithout: : OUT std_logic_vector (15 downto 0); Result Cout : OUT std_logic); --carry out bit of operation end ArithmeticUnit16bit; Note: 8-bit multiplier has only 16 bits as output, the carry out of arithmetic unit must be 0 when a multiplication operation is performed. The carry out of this unit must be 1 after incremental operation is performed when current A's value is 0xFFFF (Overflow case) For example: if A =0xFFFF, then A = A +1 = 0x0000 and carry out = 1 The following table describes this unit's behavior: Op_Sel(1 downto 0) Operation 00 A B 01 A +B 10 A-B Increment A (A +1) 11 Report: VHDL code and waveforms

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts