Question: NEED DESIGN CODE, TESTBENCH CODE AND WAVEFORMS NEED VHDL DESIGN CODE, TESTBENCH CODE AND WAVEFORMS PLEASE ANSWER IN VHDL Problem 1: (30 pts) Design a

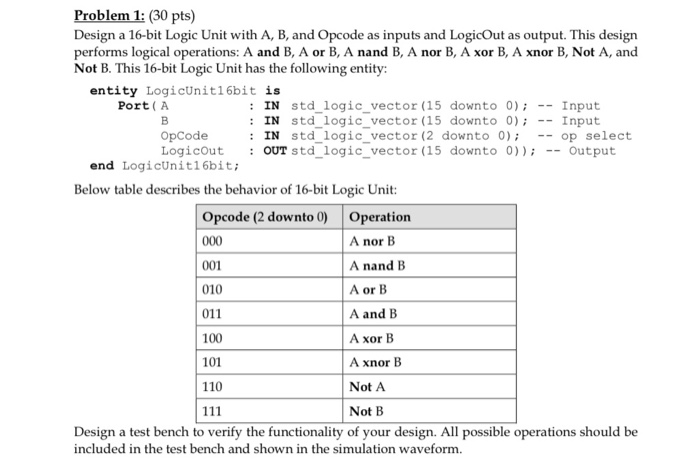

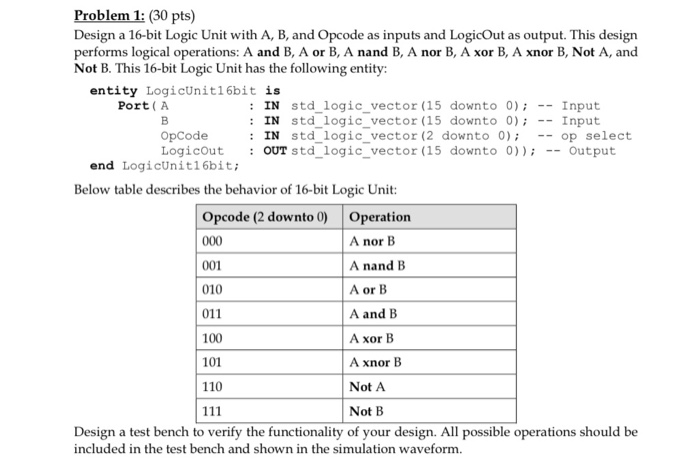

Problem 1: (30 pts) Design a 16-bit Logic Unit with A, B, and Opcode as inputs and LogicOut as output. This design performs logical operations: A and B, A or B, A nand B, A nor B, A xor B, A xnor B, Not A, and Not B. This 16-bit Logic Unit has the following entity: entity LogicUnit16bit is Port (A IN std_logic_vector (15 downto 0); -- Input IN std_logic_vector (15 downto 0); -- Input : IN std logic vector (2 downto 0); -- op select Logicout : OUT std_logic_vector (15 downto 0)); -- Output end LogicUnit16bit; Below table describes the behavior of 16-bit Logic Unit: Operation A nor B Opcode (2 downto 0) 000 001 010 Anand B 011 100 101 A or B A and B A xor B A xnor B Not A 110 Not B Design a test bench to verify the functionality of your design. All possible operations should be included in the test bench and shown in the simulation waveform. Problem 1: (30 pts) Design a 16-bit Logic Unit with A, B, and Opcode as inputs and LogicOut as output. This design performs logical operations: A and B, A or B, A nand B, A nor B, A xor B, A xnor B, Not A, and Not B. This 16-bit Logic Unit has the following entity: entity LogicUnit16bit is Port (A IN std_logic_vector (15 downto 0); -- Input IN std_logic_vector (15 downto 0); -- Input : IN std logic vector (2 downto 0); -- op select Logicout : OUT std_logic_vector (15 downto 0)); -- Output end LogicUnit16bit; Below table describes the behavior of 16-bit Logic Unit: Operation A nor B Opcode (2 downto 0) 000 001 010 Anand B 011 100 101 A or B A and B A xor B A xnor B Not A 110 Not B Design a test bench to verify the functionality of your design. All possible operations should be included in the test bench and shown in the simulation waveform

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts