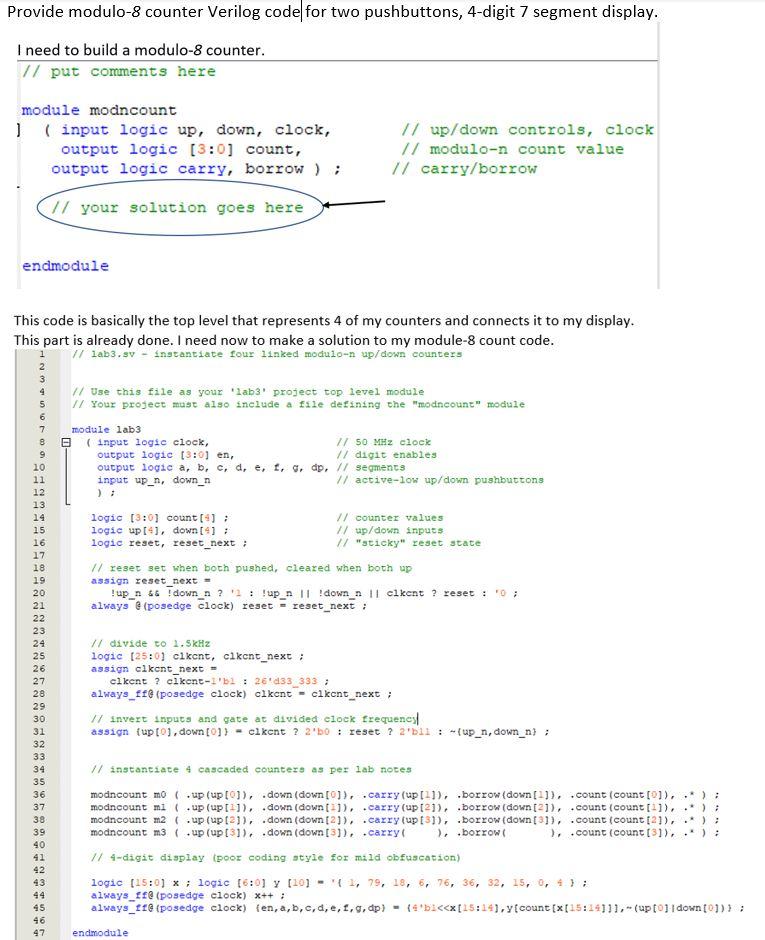

Question: // put comments here module modncount ( input logic up, down, clock, // up/down controls, clock output logic [3:0] count, // modulo-9 count value output

![clock, // up/down controls, clock output logic [3:0] count, // modulo-9 count](https://dsd5zvtm8ll6.cloudfront.net/si.experts.images/questions/2024/09/66f51bd0486d1_47166f51bcfc8e6c.jpg)

// put comments here

module modncount ( input logic up, down, clock, // up/down controls, clock output logic [3:0] count, // modulo-9 count value output logic carry, borrow ) ; // carry/borrow

// your solution goes here

endmodule

// Use this file as your 'lab3' project top level module // Your project must also include a file defining the "modncount" module

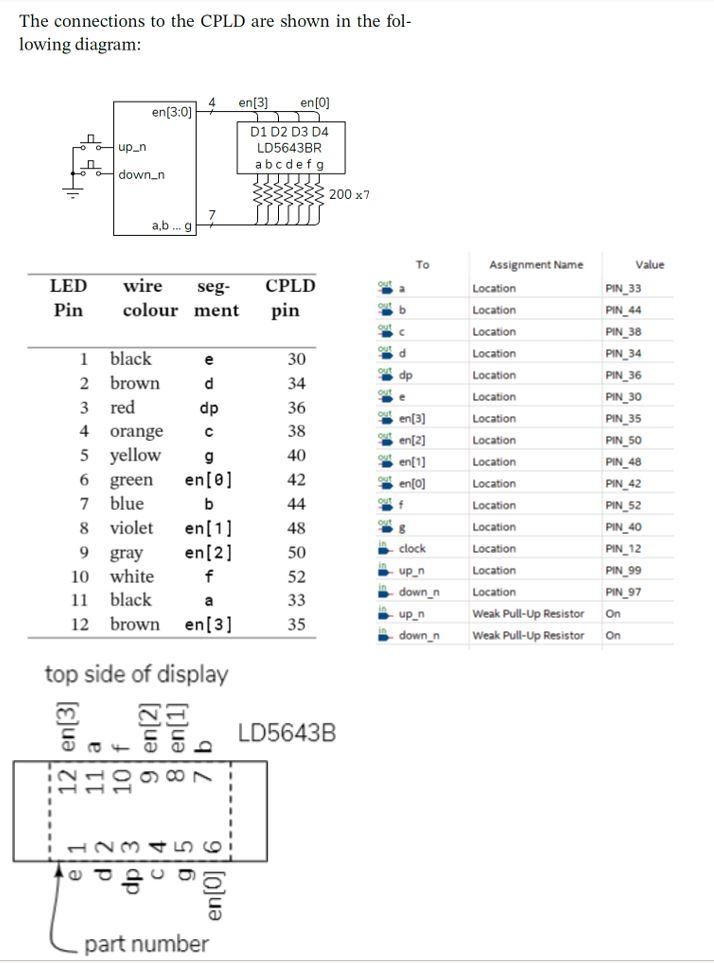

module lab3 ( input logic clock, // 50 MHz clock output logic [3:0] en, // digit enables output logic a, b, c, d, e, f, g, dp, // segments input up_n, down_n // active-low up/down pushbuttons ) ; logic [3:0] count[4] ; // counter values logic up[4], down[4] ; // up/down inputs logic reset, reset_next ; // "sticky" reset state

// reset set when both pushed, cleared when both up assign reset_next = !up_n && !down_n ? '1 : !up_n || !down_n || clkcnt ? reset : '0 ; always @(posedge clock) reset = reset_next ; // divide to 1.5kHz logic [25:0] clkcnt, clkcnt_next ; assign clkcnt_next = clkcnt ? clkcnt-1'b1 : 26'd33_333 ; always_ff@(posedge clock) clkcnt = clkcnt_next ; // invert inputs and gate at divided clock frequency assign {up[0],down[0]} = clkcnt ? 2'b0 : reset ? 2'b11 : ~{up_n,down_n} ;// instantiate 4 cascaded counters as per lab notes

modncount m0 ( .up(up[0]), .down(down[0]), .carry(up[1]), .borrow(down[1]), .count(count[0]), .* ) ; modncount m1 ( .up(up[1]), .down(down[1]), .carry(up[2]), .borrow(down[2]), .count(count[1]), .* ) ; modncount m2 ( .up(up[2]), .down(down[2]), .carry(up[3]), .borrow(down[3]), .count(count[2]), .* ) ; modncount m3 ( .up(up[3]), .down(down[3]), .carry( ), .borrow( ), .count(count[3]), .* ) ; // 4-digit display (poor coding style for mild obfuscation) logic [15:0] x ; logic [6:0] y [10] = '{ 1, 79, 18, 6, 76, 36, 32, 15, 0, 4 } ; always_ff@(posedge clock) x++ ; always_ff@(posedge clock) {en,a,b,c,d,e,f,g,dp} = {4'b1 endmodule

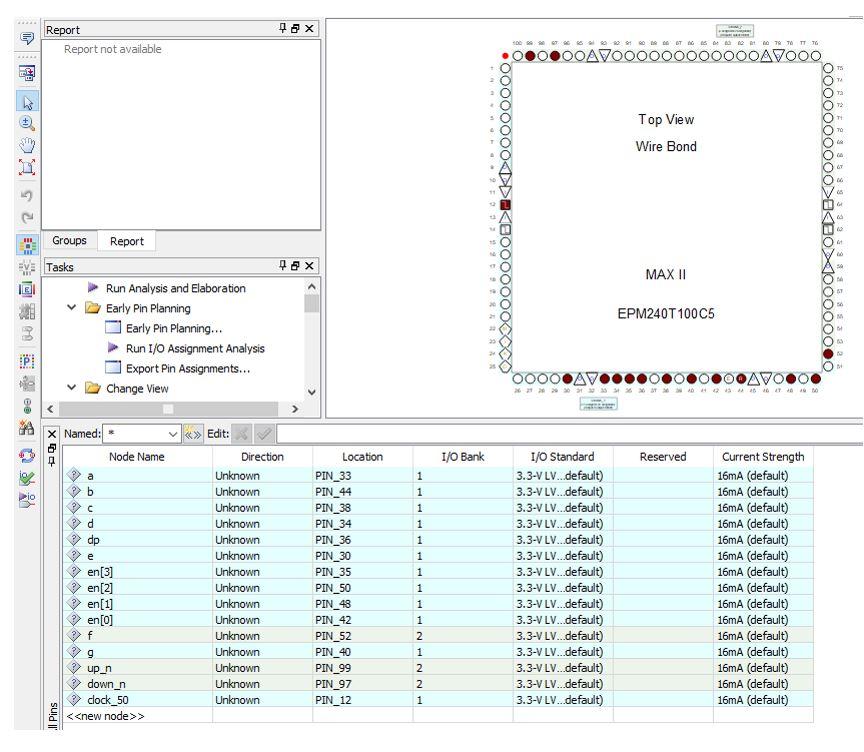

Provide modulo-8 counter Verilog code for two pushbuttons, 4-digit 7 segment display. I need to build a modulo-8 counter. 7/ put comments here module modncount 1 ( input logic up, down, clock, output logic (3:0) count, output logic carry, borrow ) ; // up/down controls, clock // modulo-n count value 1/ carry/borrow // your solution goes here endmodule This code is basically the top level that represents 4 of my counters and connects it to my display. This part is already done. I need now to make a solution to my module-8 count code. // lab3.sv - instantiate four linked modulo-n up/down counters 1 2 3 // Use this file as your 'lab3' project top level module // Your project must also include a file defining the "modcount" module module lab3 (input logic clock, // 50 MHz clock output logic (3:0) en, // digit enables output logic a, b, c, d, e, f, g, dp, // segments input up_n, down_n // active-low up/down pushbuttons 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 logic (3:0) count(); logic up ], down(); logic reset, reset_next; // counter values // up/down inputs // "sticky" reset state // reset set when both pushed, cleared when both up assign reset next = ! up_ $6 [down_n ? 2 : !up_ || !down_n 11 cikent ? reset: 0; always & (posedge clock) reset = reset_next : 25 // divide to 1. SKH logic (25:0) cikent, cikcnt_next : assign clkont_next- elkent ? clkent-i'bi : 26233_333; always_ff (posedge clock) clkent - clkcnt_next; // invert inputs and gate at divided clock frequency assign (up 101, down (01) - cikent ? 250 : reset ? 21: -(up_n, down_n) : 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 // instantiate 4 cascaded counters as per la notes modncount mo (up (upto), down (down[0]), carry (up!11), .borrow (down[1]), .count (count [0]), modncount mi (up (up [?]), .down (down (1), .carry (up (21), borrow (down (21), .count (count [1]), ); modncount m2 (up (up [2]), .down (down [21), .carry up t31), borrow (down[3]), .count (count [21), .*); modncount m3 (-up (up [31), .down (down [3]), .carry ), borrow ), .count (count (31), ..); 1/ 4-digit display (poor coding style for mild obfuscation) logic [15:01 x ; logic (6:0) y (10) - { 1, 79, 18, 6, 76, 36, 32, 15, 0, 4); always_1f@ (posedge clock) x++; always_fr@ (posedge clock) {en, a, b, c, d, e, f, g, dp) - (Bi> + 9 9 9 9 Anou Direction Unknown Unknown Unknown Unknown Unknown Unknown Unknown Unknown Unknown Unknown Unknown Unknown Unknown Unknown Unknown Location PIN_33 PIN_44 PIN_38 PIN_34 PIN_36 PIN_30 PIN_35 PIN_50 PIN_43 PIN_42 PIN_52 PIN_40 PIN_99 PIN_97 PIN_12 1 1 1 1 1 1 1 1 1 1 I/O Standard 3.3-V LV...default) 3.3-V LV...default) 3.3-V LV...default) 3.3-V LV..default) 3.3-V LV...default) 3.3-V LV...default) 3.3-V LV..default) 3.3-V LV...default) 3.3-V LV...default) 3.3-V LV..default) 3.3-V LV..default) 3.3-V LV. default) 3.3-V LV. default) 3.3-V LV...default) 3.3-V LV...default) Current Strength 16mA (default) 16mA (default) 16mA (default) 16mA (default) 16mA (default) 16mA (default) 16mA (default) 16mA (default) 16mA (default) 16mA (default) 16mA (default) 16mA (default) 16mA (default) 16mA (default) 16mA (default) NNN 1 ll Pins Provide modulo-8 counter Verilog code for two pushbuttons, 4-digit 7 segment display. I need to build a modulo-8 counter. 7/ put comments here module modncount 1 ( input logic up, down, clock, output logic (3:0) count, output logic carry, borrow ) ; // up/down controls, clock // modulo-n count value 1/ carry/borrow // your solution goes here endmodule This code is basically the top level that represents 4 of my counters and connects it to my display. This part is already done. I need now to make a solution to my module-8 count code. // lab3.sv - instantiate four linked modulo-n up/down counters 1 2 3 // Use this file as your 'lab3' project top level module // Your project must also include a file defining the "modcount" module module lab3 (input logic clock, // 50 MHz clock output logic (3:0) en, // digit enables output logic a, b, c, d, e, f, g, dp, // segments input up_n, down_n // active-low up/down pushbuttons 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 logic (3:0) count(); logic up ], down(); logic reset, reset_next; // counter values // up/down inputs // "sticky" reset state // reset set when both pushed, cleared when both up assign reset next = ! up_ $6 [down_n ? 2 : !up_ || !down_n 11 cikent ? reset: 0; always & (posedge clock) reset = reset_next : 25 // divide to 1. SKH logic (25:0) cikent, cikcnt_next : assign clkont_next- elkent ? clkent-i'bi : 26233_333; always_ff (posedge clock) clkent - clkcnt_next; // invert inputs and gate at divided clock frequency assign (up 101, down (01) - cikent ? 250 : reset ? 21: -(up_n, down_n) : 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 // instantiate 4 cascaded counters as per la notes modncount mo (up (upto), down (down[0]), carry (up!11), .borrow (down[1]), .count (count [0]), modncount mi (up (up [?]), .down (down (1), .carry (up (21), borrow (down (21), .count (count [1]), ); modncount m2 (up (up [2]), .down (down [21), .carry up t31), borrow (down[3]), .count (count [21), .*); modncount m3 (-up (up [31), .down (down [3]), .carry ), borrow ), .count (count (31), ..); 1/ 4-digit display (poor coding style for mild obfuscation) logic [15:01 x ; logic (6:0) y (10) - { 1, 79, 18, 6, 76, 36, 32, 15, 0, 4); always_1f@ (posedge clock) x++; always_fr@ (posedge clock) {en, a, b, c, d, e, f, g, dp) - (Bi> + 9 9 9 9 Anou Direction Unknown Unknown Unknown Unknown Unknown Unknown Unknown Unknown Unknown Unknown Unknown Unknown Unknown Unknown Unknown Location PIN_33 PIN_44 PIN_38 PIN_34 PIN_36 PIN_30 PIN_35 PIN_50 PIN_43 PIN_42 PIN_52 PIN_40 PIN_99 PIN_97 PIN_12 1 1 1 1 1 1 1 1 1 1 I/O Standard 3.3-V LV...default) 3.3-V LV...default) 3.3-V LV...default) 3.3-V LV..default) 3.3-V LV...default) 3.3-V LV...default) 3.3-V LV..default) 3.3-V LV...default) 3.3-V LV...default) 3.3-V LV..default) 3.3-V LV..default) 3.3-V LV. default) 3.3-V LV. default) 3.3-V LV...default) 3.3-V LV...default) Current Strength 16mA (default) 16mA (default) 16mA (default) 16mA (default) 16mA (default) 16mA (default) 16mA (default) 16mA (default) 16mA (default) 16mA (default) 16mA (default) 16mA (default) 16mA (default) 16mA (default) 16mA (default) NNN 1 ll Pins Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock