Question: Q1. Basic pipelining Consider the following MIPS code 11: LUI R1, 0x1234 I2: ORI R1, R1, 0x0010 I3: LW I4: LW I5: SUB R4, R3,

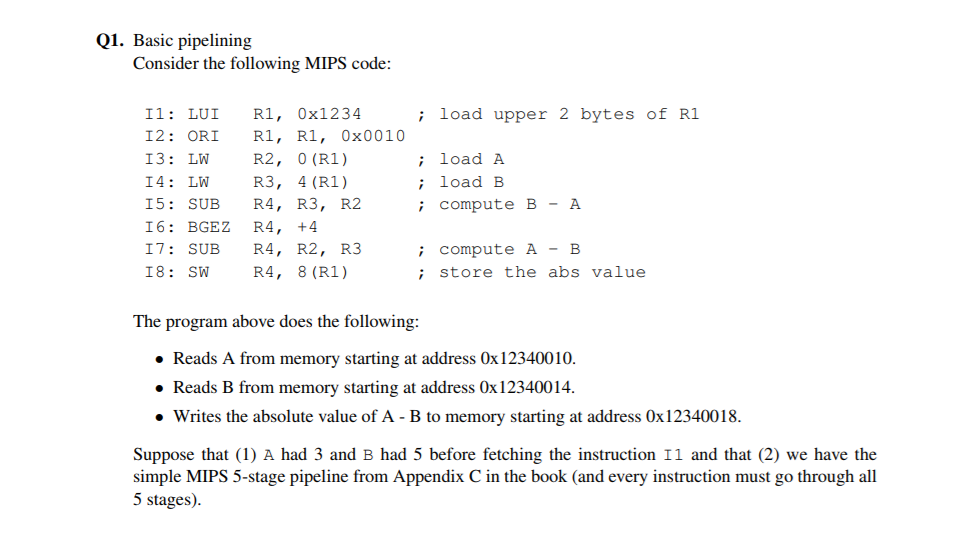

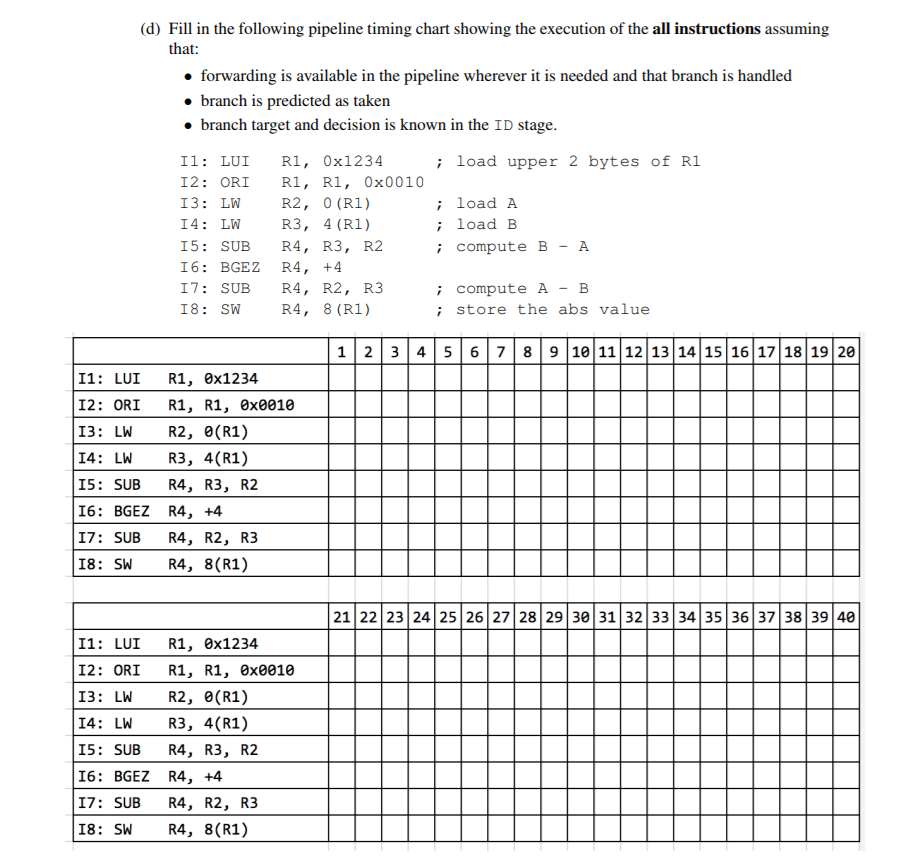

Q1. Basic pipelining Consider the following MIPS code 11: LUI R1, 0x1234 I2: ORI R1, R1, 0x0010 I3: LW I4: LW I5: SUB R4, R3, R2 I6: BGEZ R4, +4 17: SUB R4, R2, R3 I8: SW ; load upper 2 bytes of R1 R2, 0 (R1) R3, 4 (R1) ;load A ; load B ;compute B-A ;compute A -B ; store the abs value R4, 8 (R1) The program above does the following . Reads A from memory starting at address 0x 12340010 . Reads B from memory starting at address 0x12340014 . Writes the absolute value of A B to memory starting at address 0x12340018 Suppose that (1) A had 3 and B had 5 before fetching the instruction I1 and that (2) we have the simple MIPS 5-stage pipeline from Appendix C in the book (and every instruction must go through all 5 stages)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts