Question: Consider a pipeline with forwarding, hazard detection, and 1 delay slot for branches. The pipeline is the typical 5-stage IF, ID, EX, MEM, WB MIPS

Consider a pipeline with forwarding, hazard detection, and 1 delay slot for branches. The pipeline is the typical 5-stage IF, ID, EX, MEM, WB MIPS design.

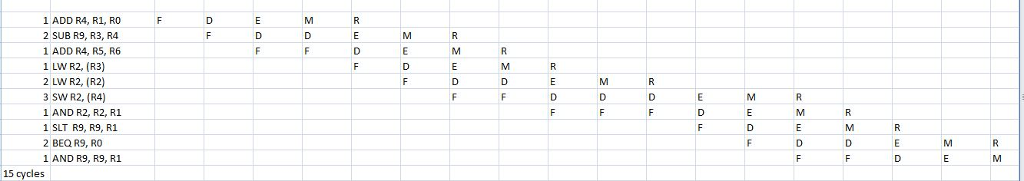

For the below code, complete the pipeline diagram below (instructions on the left, cycles on top) for the code. Insert the characters IF, ID, EX, MEM, WB for each instruction in the boxes.

Assume that there two levels of bypassing, that the second half of the decode stage performs a read of source registers, and that the first half of the write-back stage writes to the register file.

I0: ADD R4 = R1 + R0; I1: SUB R9 = R3 - R4; I2: ADD R4 = R5 + R6; I3: LDW R2 = MEM[R3 + 100]; I4: LDW R2 = MEM[R2 + 0]; I5: STW MEM[R4 + 100] = R2; I6: AND R2 = R2 & R1; I7: BEQ R9 == R1, Target; I8: AND R9 = R9 & R1;

Draw the table and find the total cycles in above program. I calculated and found its 15 cycles. I wanted to confirm this. So please solve above program and find total cycles by drawing table.

My Solution

1 ADD R4, R1, RO 2 SUB R9, R3, R4 1 ADD R4, R5, R6 1 LW R2, (R3) 2 LW R2, (R2) 3 SW R2, (R4) 1 AND R2, R2, R1 1 SLT R9, R9, R1 2 BEQ R9, RO 1 AND R9, R9, R1 8 0 2 2 2 15 cycles

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts