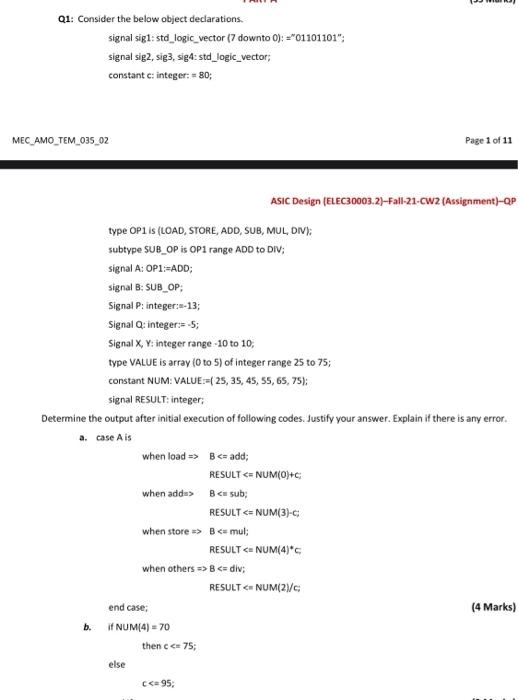

Question: Q1: Consider the below object declarations. signal sig1:std_logic_vector (7 downto 0); = 01101101; signal sig2, sig3, sig4: std_logic_vector; constant c: integer = 80; MEC_AMO_TEM_035_02 Page

Q1: Consider the below object declarations. signal sig1:std_logic_vector (7 downto 0); = 01101101"; signal sig2, sig3, sig4: std_logic_vector; constant c: integer = 80; MEC_AMO_TEM_035_02 Page 1 of 11 ASIC Design (ELEC30003.2)-Fall-21-CW2 (Assignment)-OP type OP1 IS (LOAD, STORE, ADD, SUB, MUL, DIV); subtype SUB_OP is OP1 range ADD to DIV; signal A: OP1:=ADD; signal B: SUB_OP Signal P: integer:--13; Signal Q:integer; Signal X, Y: integer range -10 to 10, type VALUE is array (0 to 5) of integer range 25 to 75; constant NUM:VALUE: (25, 35, 45, 55, 65, 75); signal RESULT: integer Determine the output after initial execution of following codes. Justify your answer. Explain if there is any error. case Ais when load=> B BC sub RESULT Bc mul; RESULTS. NUM(4) when others ->

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts