Question: Q1. We have a 4-way set-associative cache. The virtual address space is 4MB, page size is 2KB, and cache block size is 1 byte. Each

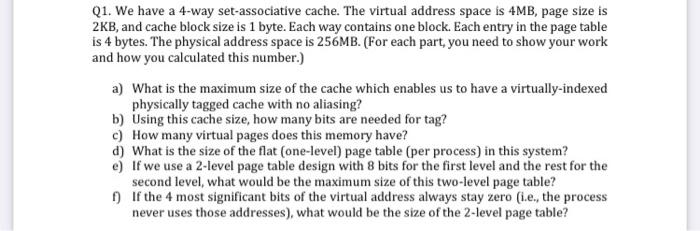

Q1. We have a 4-way set-associative cache. The virtual address space is 4MB, page size is 2KB, and cache block size is 1 byte. Each way contains one block. Each entry in the page table is 4 bytes. The physical address space is 256MB. (For each part, you need to show your work and how you calculated this number.) a) What is the maximum size of the cache which enables us to have a virtually-indexed physically tagged cache with no aliasing? b) Using this cache size, how many bits are needed for tag? c) How many virtual pages does this memory have? d) What is the size of the flat (one-level) page table (per process) in this system? e) If we use a 2-level page table design with 8 bits for the first level and the rest for the second level, what would be the maximum size of this two-level page table? f) If the 4 most significant bits of the virtual address always stay zero (i.e., the process never uses those addresses), what would be the size of the 2-level page table

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts