Question: Q.2 (a) A System-on-Chip (SoC) based on an ARM Cortex M3 processor is configured to have 2 pre-empt priority bits and 2 sub-priority bits

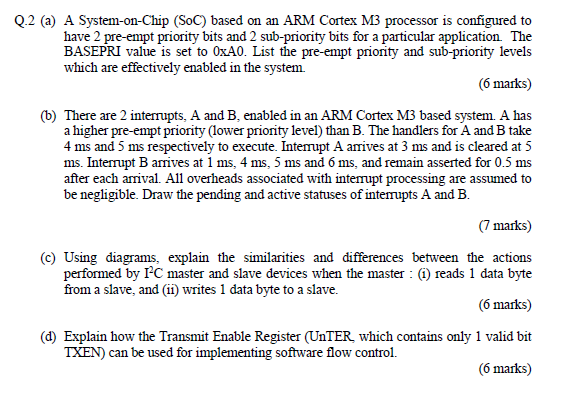

Q.2 (a) A System-on-Chip (SoC) based on an ARM Cortex M3 processor is configured to have 2 pre-empt priority bits and 2 sub-priority bits for a particular application. The BASERRI value is set to OxA0. List the pre-empt priority and sub-priority levels which are effectively enabled in the system. (6 marks) (b) There are 2 interrupts, A and B. enabled in an ARM Cortex M3 based system. A has a higher pre-empt priority (lower priority level) than B. The handlers for A and B take 4 ms and 5 ms respectively to execute. Interrupt A arrives at 3 ms and is cleared at 5 ms. Interrupt B arrives at 1 ms, 4 ms, 5 ms and 6 ms, and remain asserted for 0.5 ms after each arrival. All overheads associated with interrupt processing are assumed to be negligible. Draw the pending and active statuses of interrupts A and B. (7 marks) (c) Using diagrams, explain the similarities and differences between the actions performed by IC master and slave devices when the master: (1) reads 1 data byte from a slave, and (ii) writes 1 data byte to a slave. (6 marks) (d) Explain how the Transmit Enable Register (UnTER which contains only 1 valid bit TXEN) can be used for implementing software flow control. (6 marks)

Step by Step Solution

There are 3 Steps involved in it

a The preempt priority and subpriority levels effectively enabled in the system with 2 preempt prior... View full answer

Get step-by-step solutions from verified subject matter experts