Question: Q3 Finite State Machine Using a ROM based finite state machine (FSM), design a bi-directional repetitive 3-bit modulo-6 (0, 1, 2, 3, 4, 5) counter

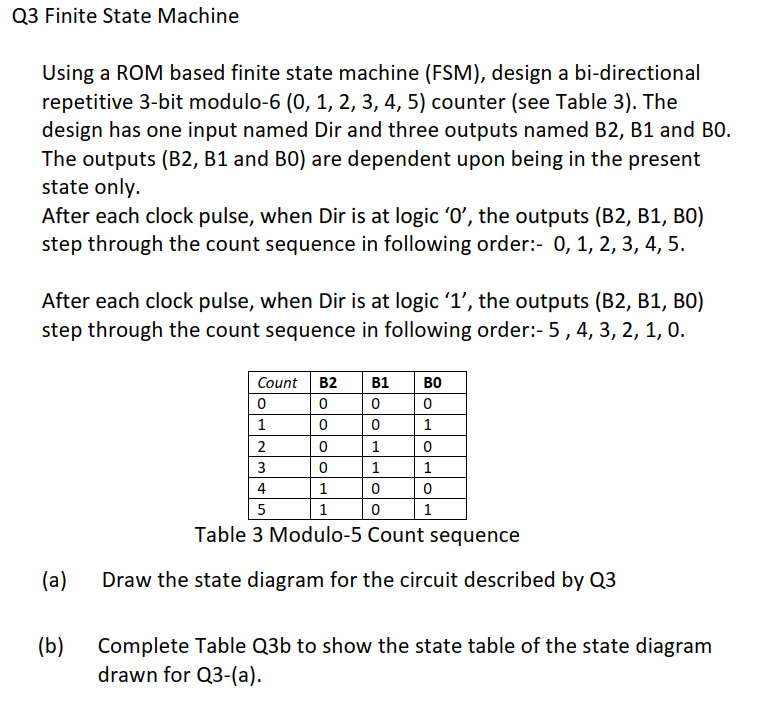

Q3 Finite State Machine Using a ROM based finite state machine (FSM), design a bi-directional repetitive 3-bit modulo-6 (0, 1, 2, 3, 4, 5) counter (see Table 3). The design has one input named Dir and three outputs named B2, B1 and BO. The outputs (B2, B1 and BO) are dependent upon being in the present state only. After each clock pulse, when Dir is at logic O, the outputs (B2, B1, BO) step through the count sequence in following order:- 0, 1, 2, 3, 4, 5. After each clock pulse, when Dir is at logic '1', the outputs (B2, B1, BO) step through the count sequence in following order:-5,4,3, 2, 1, 0. Count B2 B1 BO 0 O 0 0 1 0 0 1 2 0 1 0 3 0 1 1 4 1 0 0 5 1 0 1 Table 3 Modulo-5 Count sequence (a) Draw the state diagram for the circuit described by Q3 (b) Complete Table Q3b to show the state table of the state diagram drawn for Q3-(a)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts