Question: Question 1 Design of FSMs Involves: . Defining states . Defining transitions between states . Optimization / minimization To describe an FSM in VHDL, the

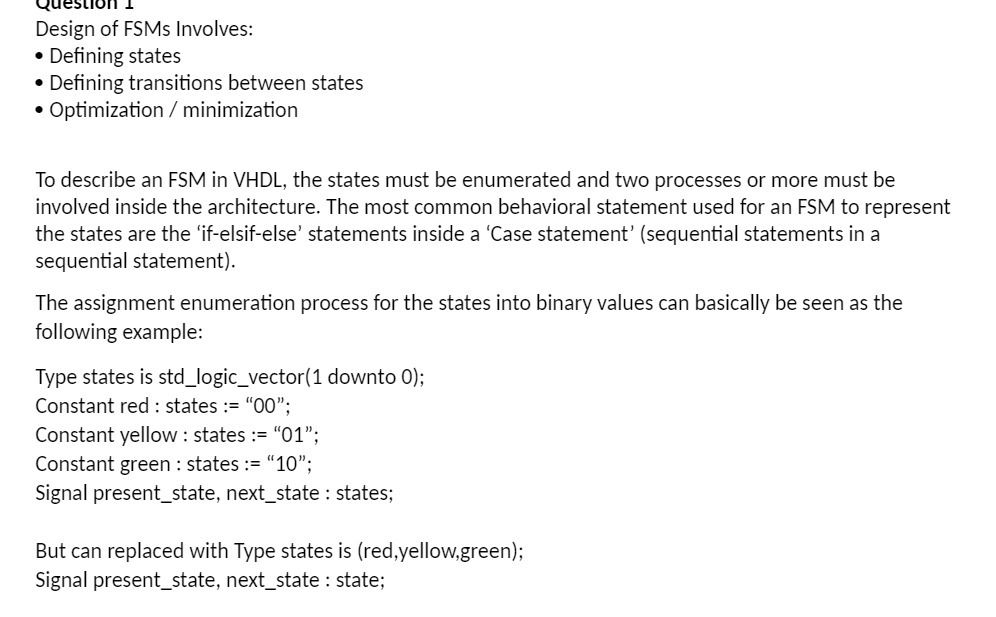

Question 1 Design of FSMs Involves: . Defining states . Defining transitions between states . Optimization / minimization To describe an FSM in VHDL, the states must be enumerated and two processes or more must be involved inside the architecture. The most common behavioral statement used for an FSM to represent the states are the 'if-elsif-else' statements inside a 'Case statement' (sequential statements in a sequential statement). The assignment enumeration process for the states into binary values can basically be seen as the following example: Type states is std_logic_vector(1 downto 0); Constant red : states := "00"; Constant yellow : states := "01"; Constant green : states := "10"; Signal present_state, next_state : states; But can replaced with Type states is (red, yellow,green); Signal present_state, next_state : state

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts