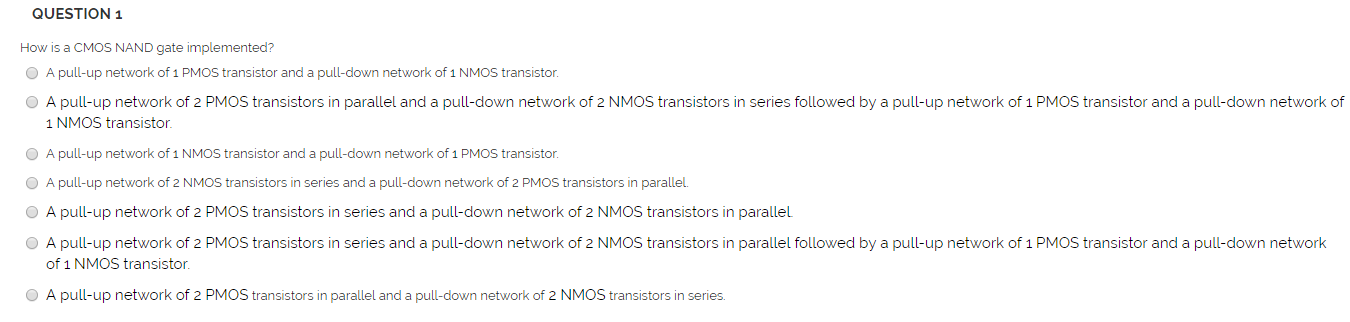

Question: QUESTION 1 How is a CMOS NAND gate implemented? A pull-up network of 1 PMOS transistor and a pull-down network of 1 NMOS transistor. O

QUESTION 1 How is a CMOS NAND gate implemented? A pull-up network of 1 PMOS transistor and a pull-down network of 1 NMOS transistor. O A pull-up network of 2 PMOS transistors in parallel and a pull-down network of 2 NMOS transistors in series followed by a pull-up network of 1 PMOS transistor and a pull-down network of 1 NMOS transistor A pull-up network of 1 NMOS transistor and a pull-down network of 1 PMOS transistor. O A pull-up network of 2 NMOS transistors in series and a pull-down network of 2 PMOS transistors in parallel A pull-up network of 2 PMOS transistors in series and a pull-down network of 2 NMOS transistors in parallel O A pull-up network of 2 PMOS transistors in series and a pull-down network of 2 NMOS transistors in parallel followed by a pull-up network of 1 PMOS transistor and a pull-down network of 1 NMOS transistor. O A pull-up network of 2 PMOS transistors in parallel and a pull-down network of 2 NMOS transistors in series

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts