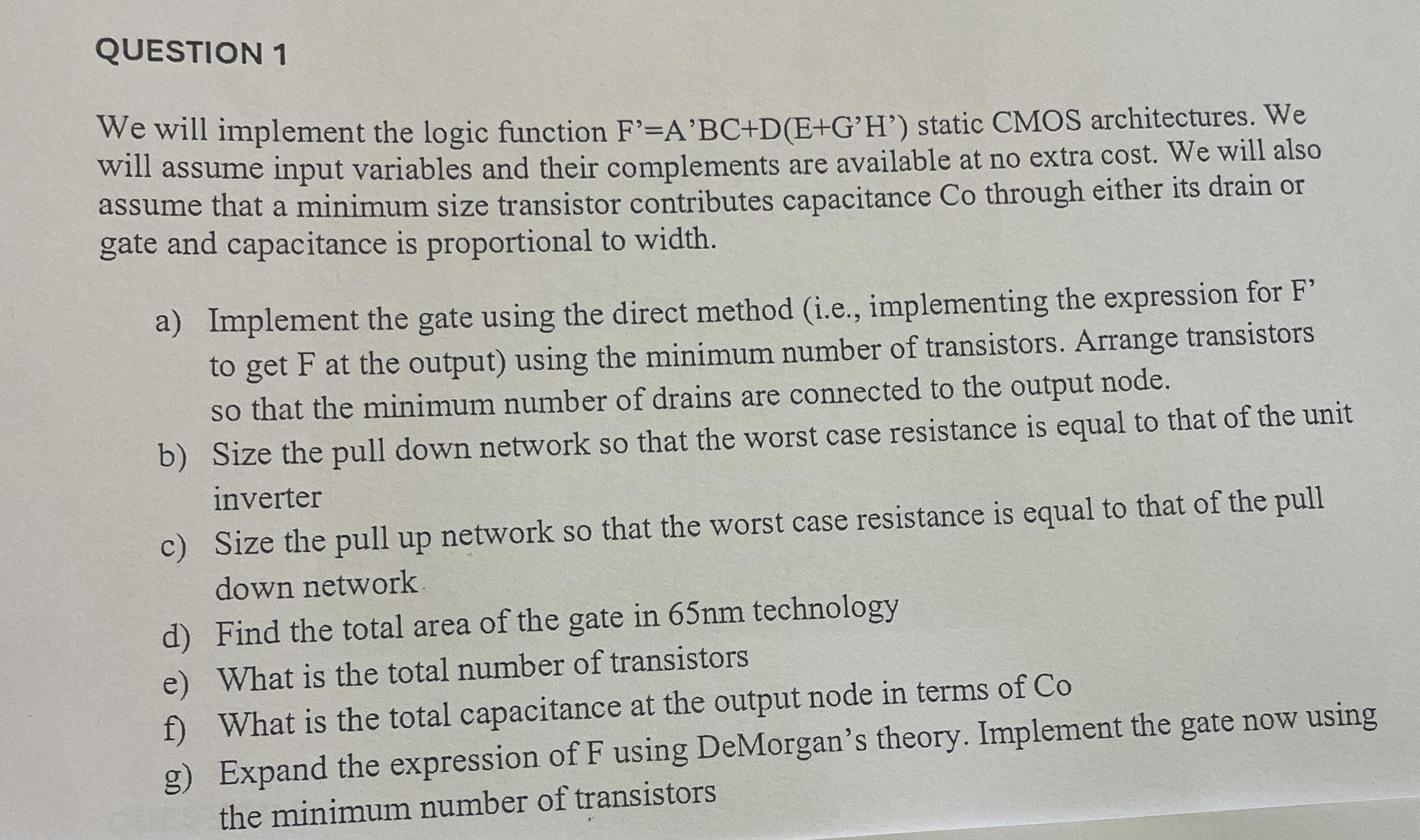

Question: QUESTION 1 We will implement the logic function F ' = A ' B C + D ( E + G ' H ' )

QUESTION

We will implement the logic function static CMOS architectures. We will assume input variables and their complements are available at no extra cost. We will also assume that a minimum size transistor contributes capacitance Co through either its drain or gate and capacitance is proportional to width.

a Implement the gate using the direct method ie implementing the expression for to get at the output using the minimum number of transistors. Arrange transistors so that the minimum number of drains are connected to the output node.

b Size the pull down network so that the worst case resistance is equal to that of the unit inverter

c Size the pull up network so that the worst case resistance is equal to that of the pull down network

d Find the total area of the gate in nm technology

e What is the total number of transistors

f What is the total capacitance at the output node in terms of Co

g Expand the expression of F using DeMorgan's theory. Implement the gate now using the minimum number of transistors

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock