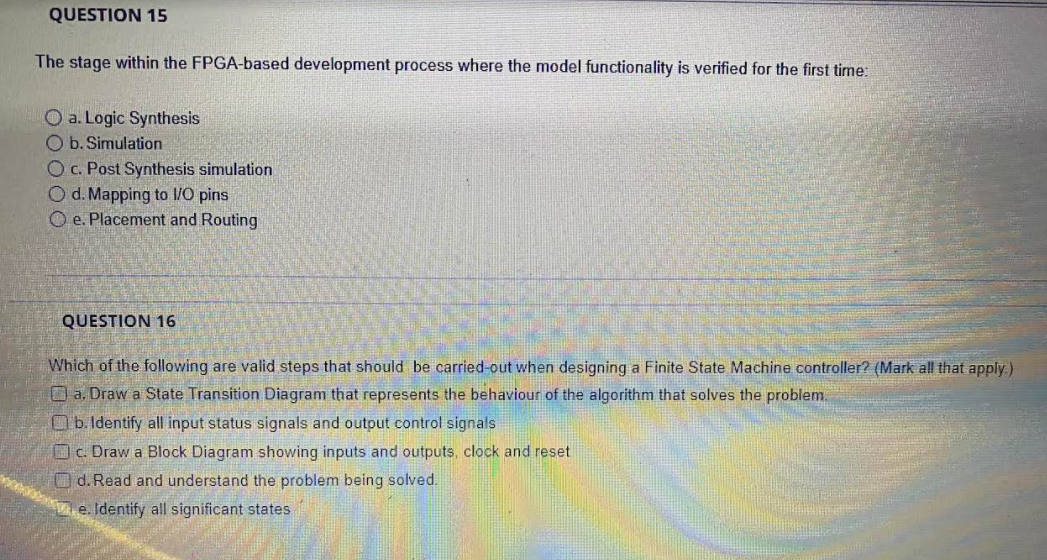

Question: QUESTION 15 The stage within the FPGA-based development process where the model functionality is verified for the first time: O a. Logic Synthesis O b.

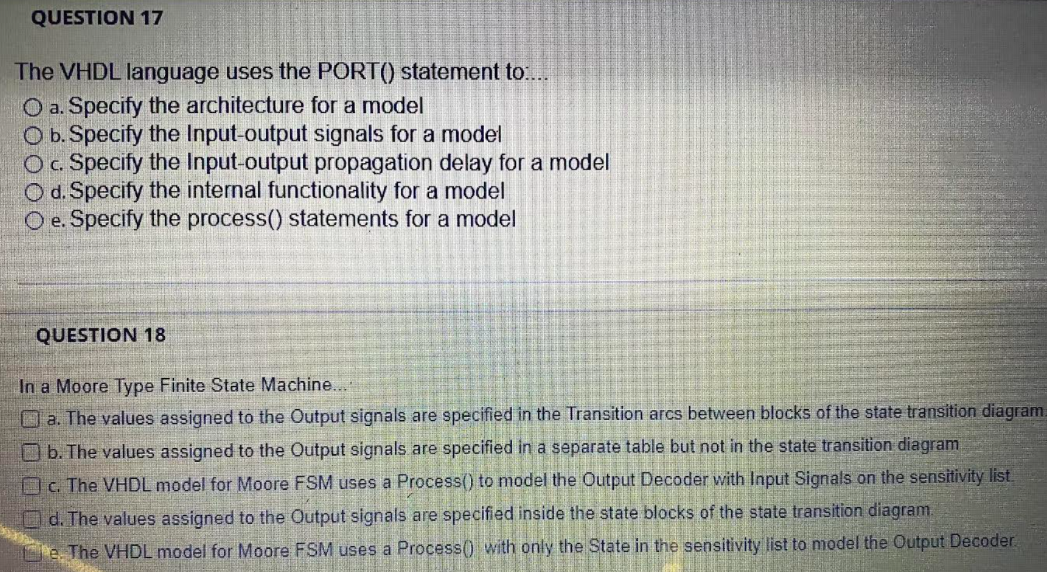

QUESTION 15 The stage within the FPGA-based development process where the model functionality is verified for the first time: O a. Logic Synthesis O b. Simulation O c. Post Synthesis simulation O d. Mapping to 1/O pins e. Placement and Routing QUESTION 16 Which of the following are valid steps that should be carried-out when designing a Finite State Machine controller? (Mark all that apply.) a. Draw a State Transition Diagram that represents the behaviour of the algorithm that solves the problem, b.Identify all input status signals and output control signals c.Draw a Block Diagram showing inputs and outputs, clock and reset d. Read and understand the problem being solved. 2. e. Identify all significant states QUESTION 17 The VHDL language uses the PORT() statement to.... O a. Specify the architecture for a model O b. Specify the Input-output signals for a model O c. Specify the Input-output propagation delay for a model O d. Specify the internal functionality for a model O e. Specify the process() statements for a model QUESTION 18 In a Moore Type Finite State Machine... O a. The values assigned to the Output signals are specified in the Transition arcs between blocks of the state transition diagram b. The values assigned to the Output signals are specified in a separate table but not in the state transition diagram c. The VHDL model for Moore FSM uses a Process() to model the Output Decoder with Input Signals on the sensitivity list d. The values assigned to the Output signals are specified inside the state blocks of the state transition diagram . The VHDL model for Moore FSM uses a Process() with only the State in the sensitivity list to model the Output Decoder

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts