Question: Question 2 (Computer Architecture and Cache Memory) (a) Consider a byte-addressed microprocessor where physical addresses are 22-bits. It has a 4-way associative cache of total

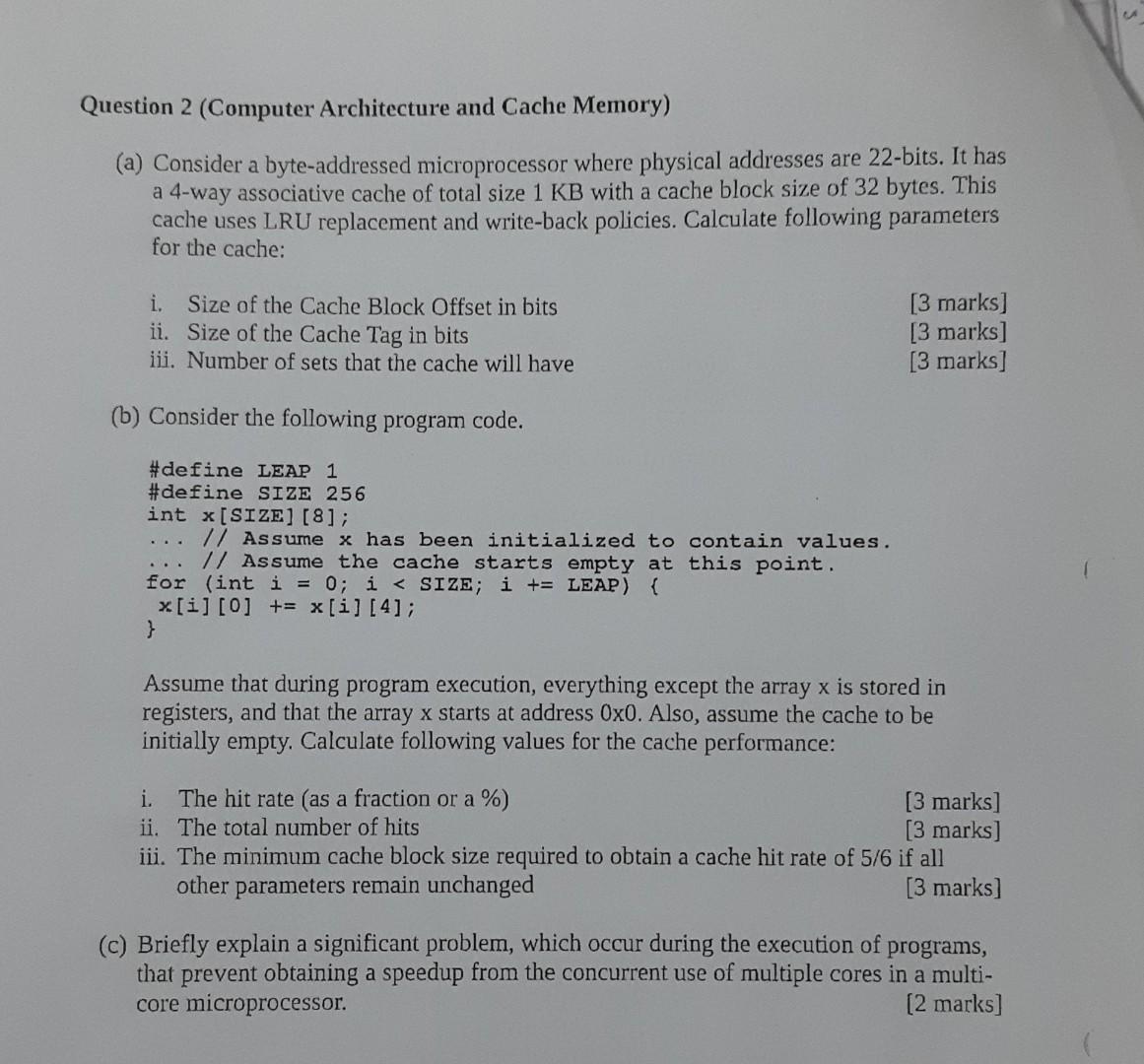

Question 2 (Computer Architecture and Cache Memory) (a) Consider a byte-addressed microprocessor where physical addresses are 22-bits. It has a 4-way associative cache of total size 1 KB with a cache block size of 32 bytes. This cache uses LRU replacement and write-back policies. Calculate following parameters for the cache: i. Size of the Cache Block Offset in bits ii. Size of the Cache Tag in bits iii. Number of sets that the cache will have [3 marks] [3 marks] [3 marks] (b) Consider the following program code. #define LEAP 1 #define SIZE 256 int x[SIZE] [8]; // Assume x has been initialized to contain values. // Assume the cache starts empty at this point. for (int i = 0; i

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts