Question: Question 4 Verilog conditional operators are inferred as a MUX 2 cell with both a true - case input and a false - case input.

Question

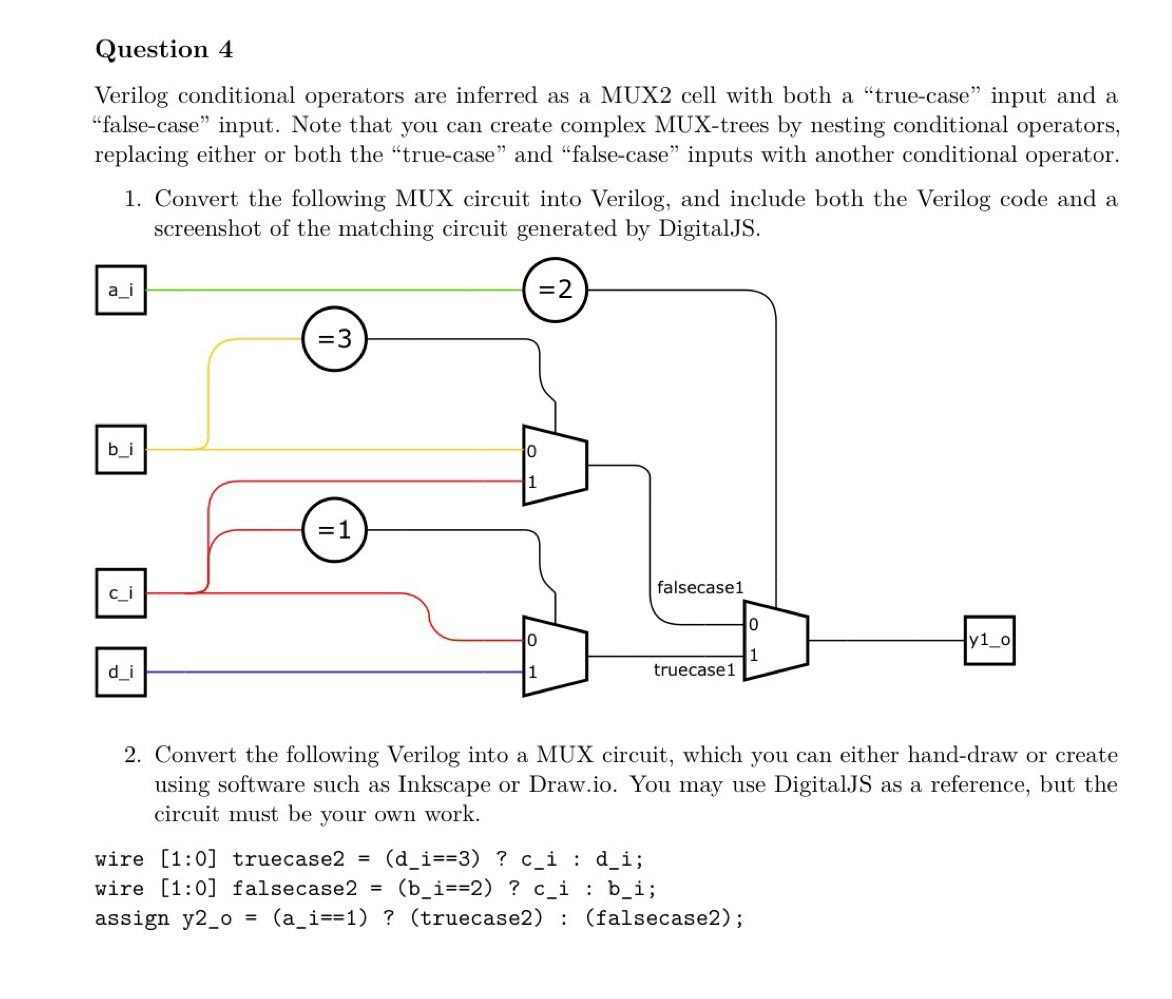

Verilog conditional operators are inferred as a MUX cell with both a "truecase" input and a "falsecase" input. Note that you can create complex MUXtrees by nesting conditional operators, replacing either or both the "truecase" and "falsecase" inputs with another conditional operator.

Convert the following MUX circuit into Verilog, and include both the Verilog code and a screenshot of the matching circuit generated by DigitalJS.

Convert the following Verilog into a MUX circuit, which you can either handdraw or create using software such as Inkscape or Draw.io You may use DigitalJS as a reference, but the circuit must be your own work.

wire : truecasedi ci : di;

wire : falsecasebi ci : bi;

assign yo aitruecase : falsecase;

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock