Question: QUESTION 5 Cache performance Suppose a computer system has a 5-stage MIPS processor, and separate data and instruction caches. The hit time of both caches

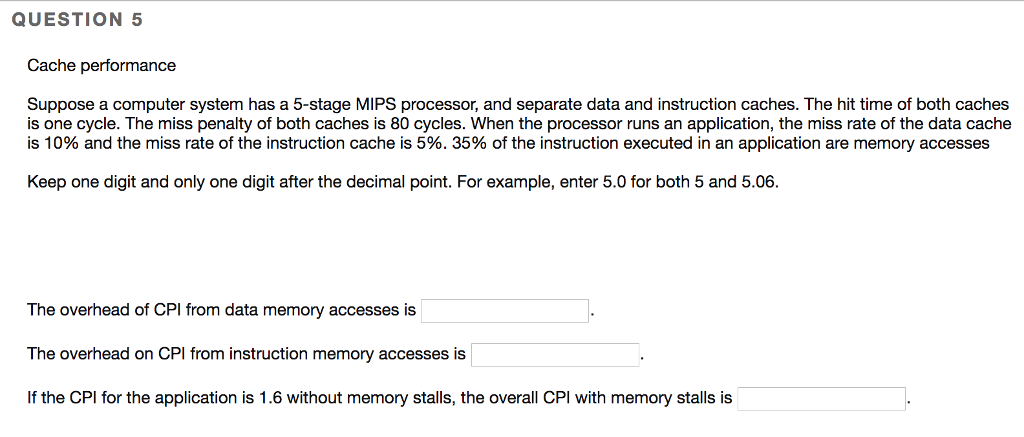

QUESTION 5 Cache performance Suppose a computer system has a 5-stage MIPS processor, and separate data and instruction caches. The hit time of both caches is one cycle. The miss penalty of both caches is 80 cycles. When the processor runs an application, the miss rate of the data cache is 10% and the miss rate of the instruction cache is 5%. 35% of the instruction executed in an application are memory accesses Keep one digit and only one digit after the decimal point. For example, enter 5.0 for both 5 and 5.06. The overhead of CPI from data memory accesses is The overhead on CPl from instruction memory accesses is If the CPI for the application is 1.6 without memory stalls, the overall CPl with memory stalls is

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts