Question: Question Part You are given a logic function to implement: X = bar ( ( bar ( ( bar ( A + B ) )

Question Part

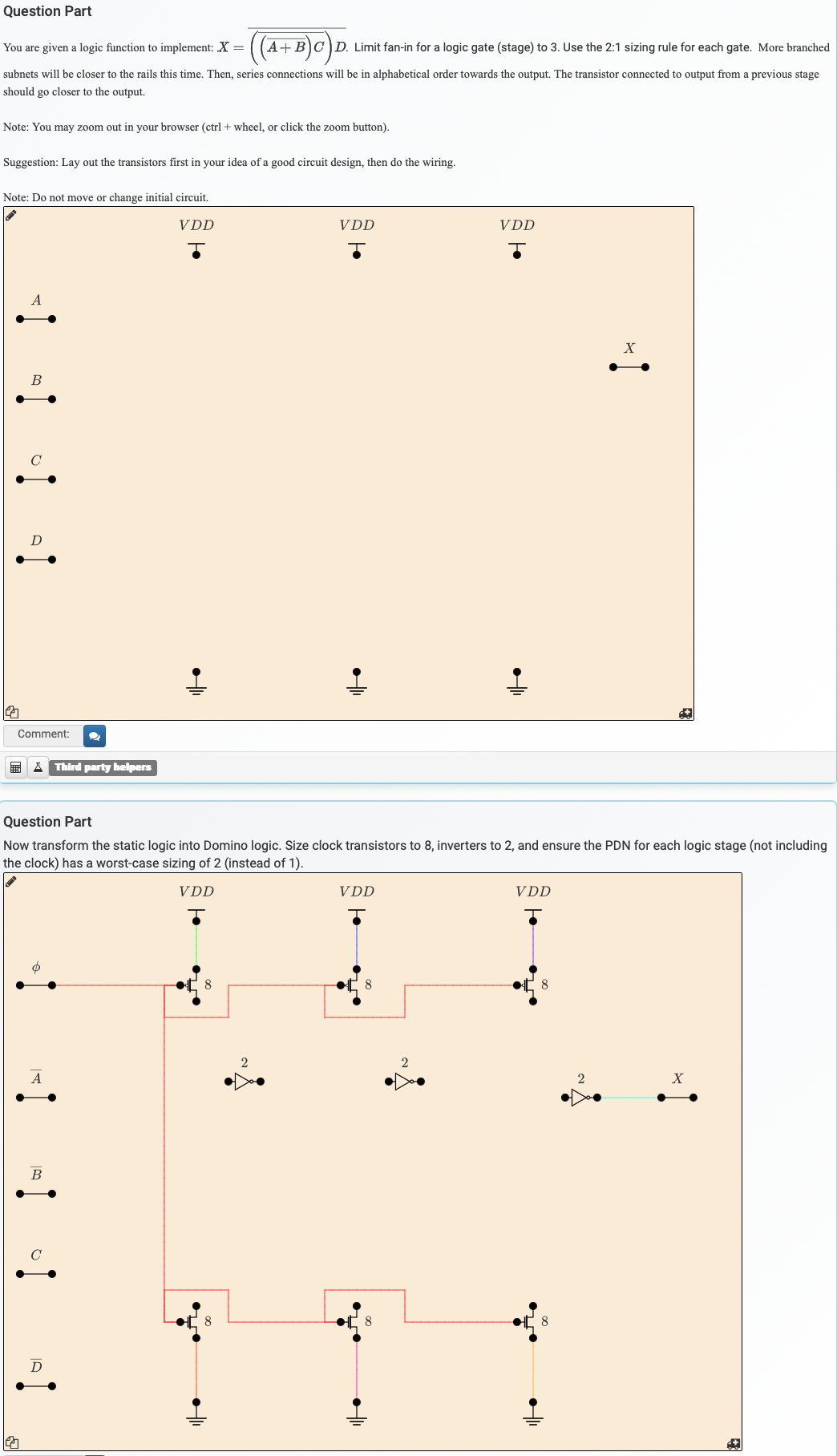

You are given a logic function to implement: X bar bar barABCD Limit fanin for a logic gate stage to Use the : sizing rule for each gate. More branched subnets will be closer to the rails this time. Then, series connections will be in alphabetical order towards the output. The transistor connected to output from a previous stage should go closer to the output.

Note: You may zoom out in your browser ctrl wheel, or click the zoom button

Suggestion: Lay out the transistors first in your idea of a good circuit design, then do the wiring.

Note: Do not move or change initial circuit.

Question Part

Now transform the static logic into Domino logic. Size clock transistors to inverters to and ensure the PDN for each logic stage not including the clock has a worstcase sizing of instead of

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock