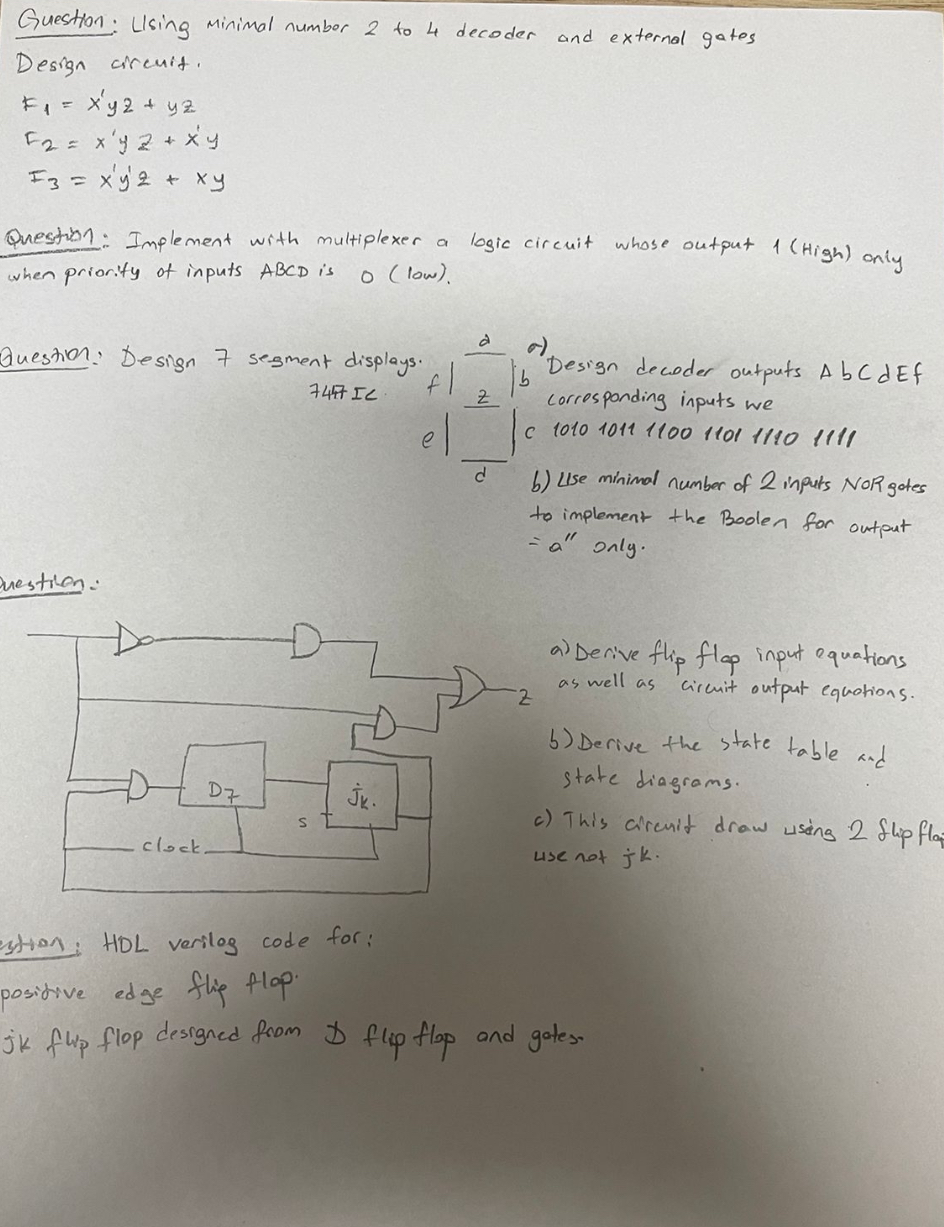

Question: Question: Using minimal number 2 to 4 decoder and external gates. Design circuit. F 1 = x ' y z + x z F 2

Question: Using minimal number to decoder and external gates.

Design circuit.

Question: Implement with multiplexer a logic circuit whose output High only when prionity of inputs ABCD is low

Question: Design segment displays.

IC

Design decoder outputs AbcdEf

corresponding inputs we

d

b Use minimal number of inputs NOR gates to implement the Boolen for output only

Question:

a Derive flip flop input equations as well as circuit output equations.

b Derive the state table and state diagrams.

c This circuit draw using flipflop use not

Question: HDL verilog code for:

apositive edge flip flop.

bjk flip flop designed from D flip flop and gates.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock