Question: .Scheduling instructions can remove some hazards that cannot be handled by hardware without pipeline stalls. Assume a 5-stage MIPS processor has all the forwarding paths

.Scheduling instructions can remove some hazards that cannot be handled by hardware without pipeline stalls. Assume a 5-stage MIPS processor has all the forwarding paths needed for better performance. The conditional branch is resolved in the ID stage. The branch is delayed and the instruction in the branch delay slot is always executed (i.e., you can place an instruction in the branch delay slot to save a cycle).

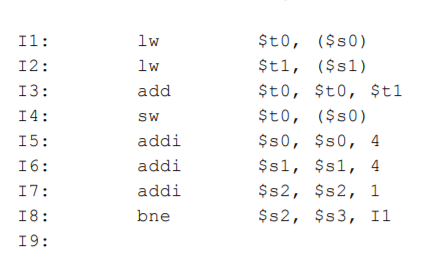

a) Schedule the instructions in the following MIPS code to reduce pipeline installs.

b) Draw a pipeline diagram from the IF stage of the first instruction to the IF stage of the same instruction in the next iteration.

I2: I3: I4: I5: I6: I7: I8: I9: ?t0, $t0, $t1 add SW addi addi addi bne ?s0, $s0, 4 ?s1, $sl, 4 $s2, $s2, 1 $s2, $s3, I1

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts