Question: Sequential Network Part A) Design a sequential network state diagram for a 2-bit counter (four states) with one input X, and one output Z. When

Sequential Network

Part A) Design a sequential network state diagram for a 2-bit counter (four states) with one input X, and one output Z. When input X = 0, the state of the circuit remains the same. When X = 1, the circuit goes to the next state: from 00 to 01, or from 01 to 10, or from 10 to 11, or from 11 to 00. Z = 1 only and only when state changes from 11 to 00. Assume q0 = 00, q1 = 01, q2 = 10, and q3 = 11.

D)Use K-map to minimize the Z, d2, and d1

E) Draw the schematic of the sequential network by using the answers form part D.

3) Use two D-Latches to design a sequence detector with one input (X), and one output (Z), capable of recognizing a sequence of 111 without overlapping. Z = 1 only and only when the pattern 111 is detected. Show your complete work (similar to Question 2).

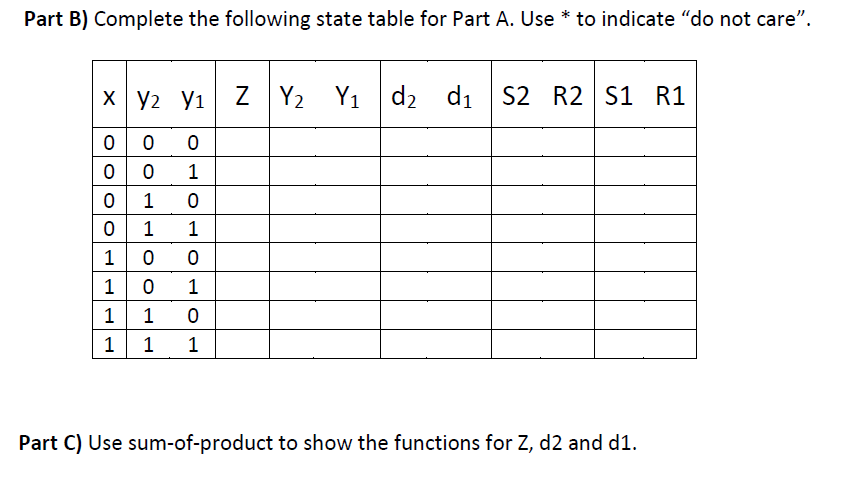

Part B) Complete the following state table for Part A. Use * to indicate "do not care". 0 01 0 1 0 0 1 1 11 0 Part C) Use sum-of-product to show the functions for Z, d2 and d1

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts