Question: Show how the example memory system in Section 9.6.4 the textbook translates a virtual address into a physical address and accesses the cache. For the

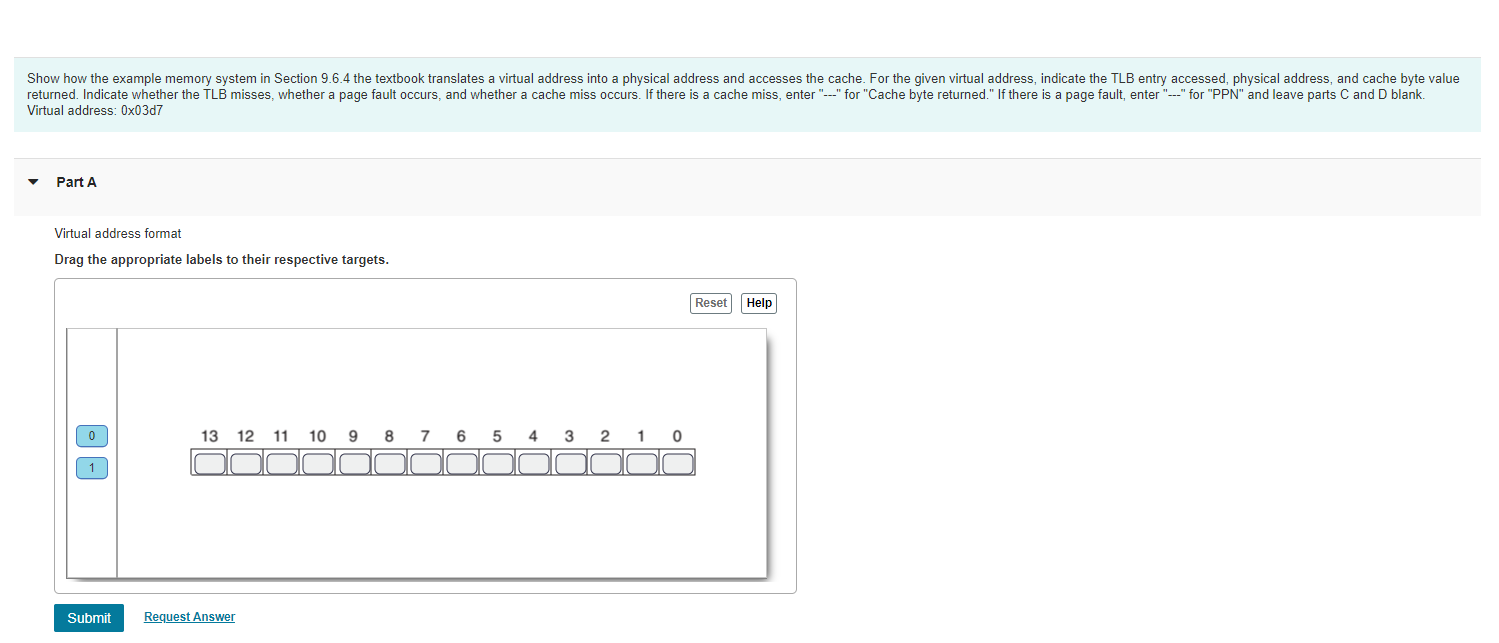

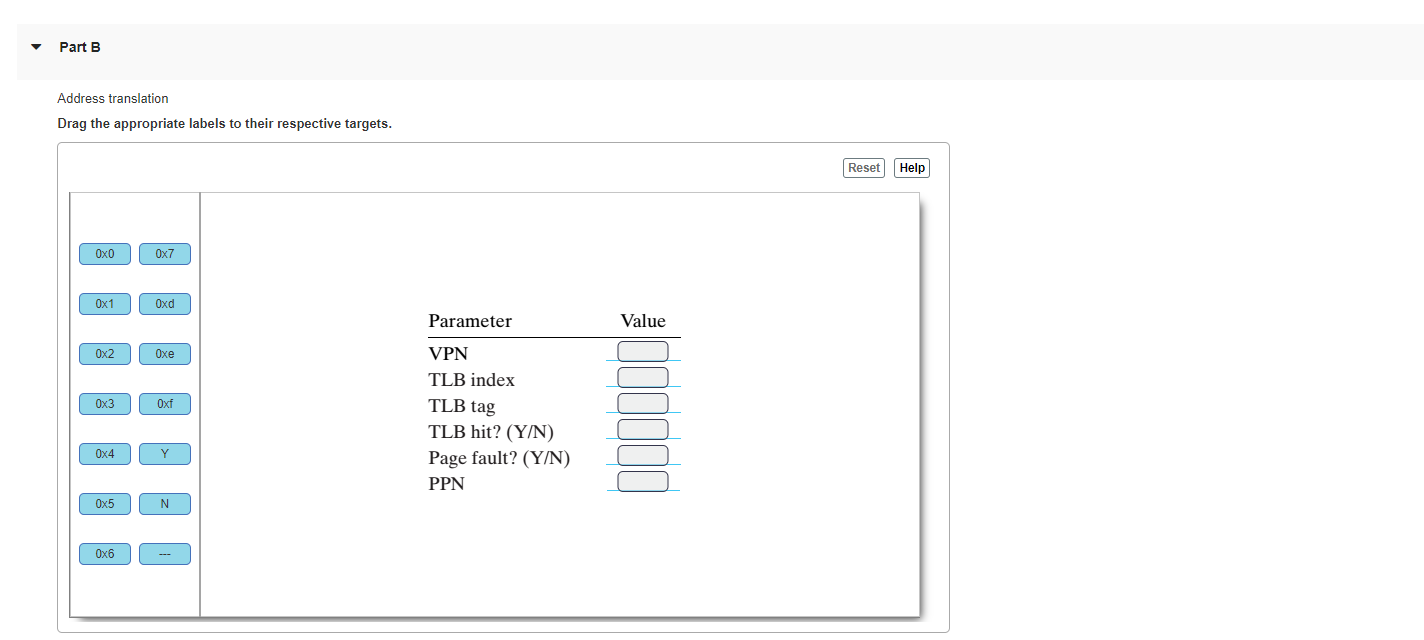

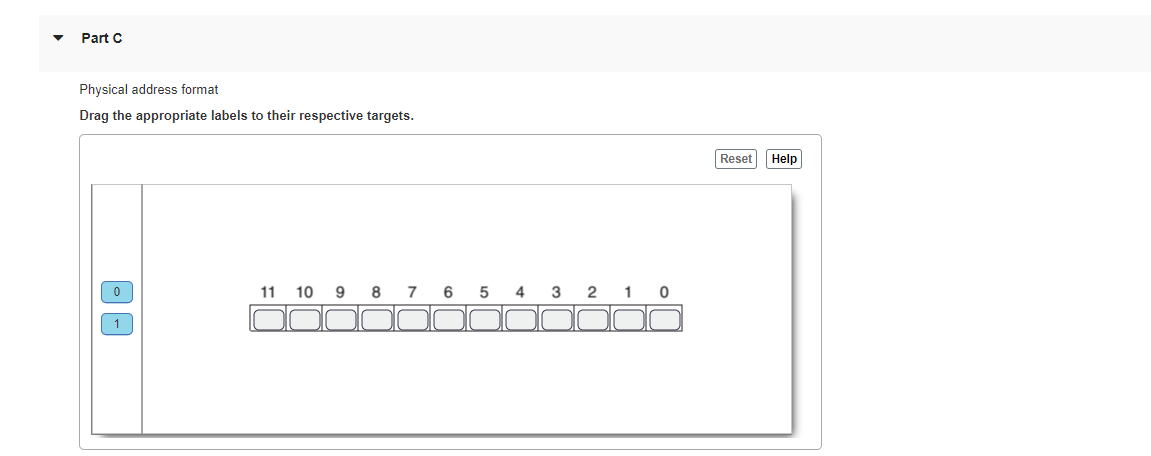

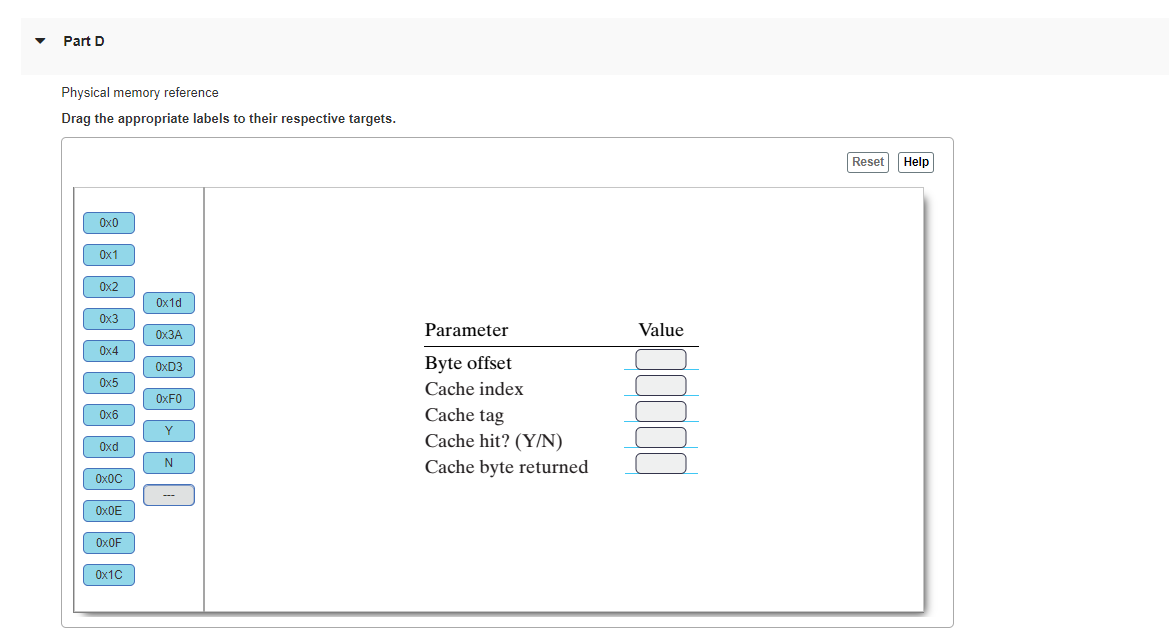

Show how the example memory system in Section 9.6.4 the textbook translates a virtual address into a physical address and accesses the cache. For the given virtual address, indicate the TLB entry accessed, physical address, and cache byte value returned. Indicate whether the TLB misses, whether a page fault occurs, and whether a cache miss occurs. If there is a cache miss, enter"--"for "Cache byte returned." If there is a page fault, enter"--"for "PPN" and leave parts C and D blank. Virtual address: 0x03d7 Part A Virtual address format Drag the appropriate labels to their respective targets. Reset Help 0 13 12 11 10 9 8 7 ? 6 5 4 3 2 10 1 Submit Request Answer Part B Address translation Drag the appropriate labels to their respective targets. Reset Help Ox0 Ox7 Ox1 Oxd Value 0x2 Oxe 0x3 Oxf Parameter VPN TLB index TLB tag TLB hit? (Y/N) Page fault? (Y/N) PPN Ox4 Y 0x5 N 0x6 Part C Physical address format Drag the appropriate labels to their respective targets. Reset Help 0 11 10 9 8 7 6 5 4 3 2 1 0 Oo 1 Part D Physical memory reference Drag the appropriate labels to their respective targets. Reset Help Ox1 Ox2 Ox 1d Ox3 Ox Parameter Value Ox4 OxD3 Ox5 OXFO Ox6 Byte offset Cache index Cache tag Cache hit? (Y/N) Cache byte returned build Y Oxd N Ox0c Ox OXOF Ox10

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts