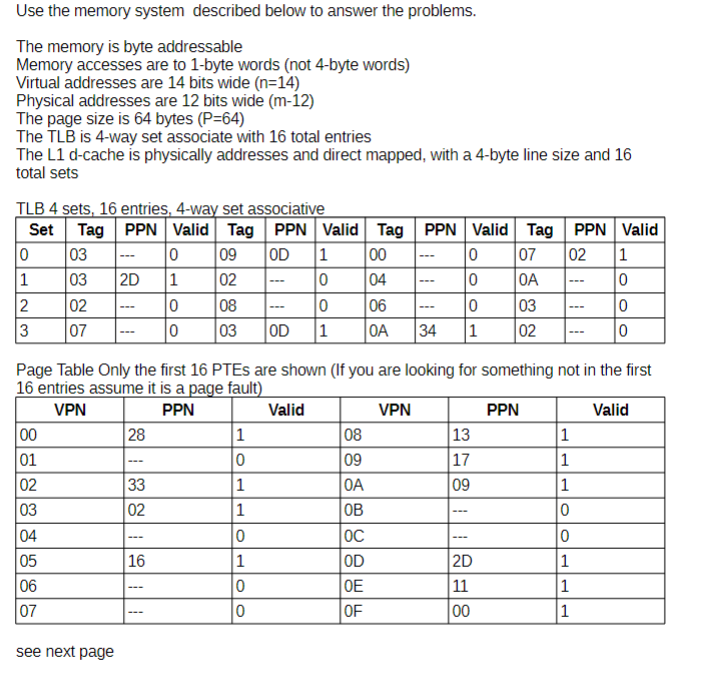

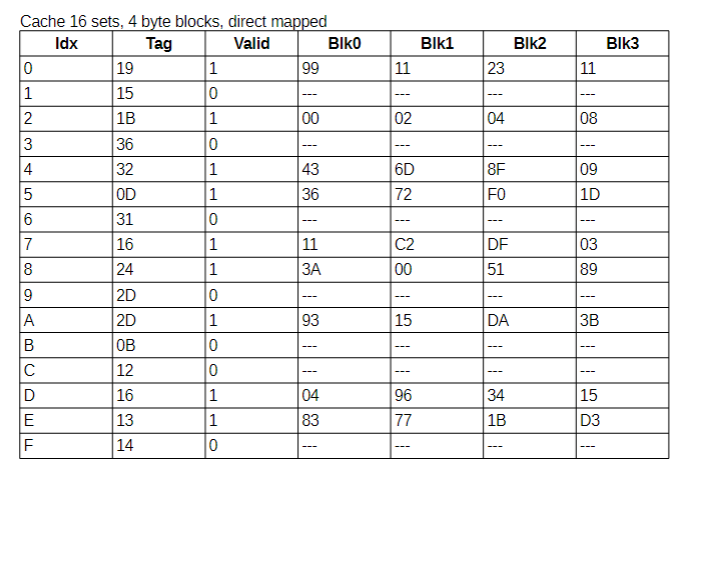

Question: Use the memory system described below to answer the problems. The memory is byte addressable Memory accesses are to 1-byte words (not 4-byte words) Virtual

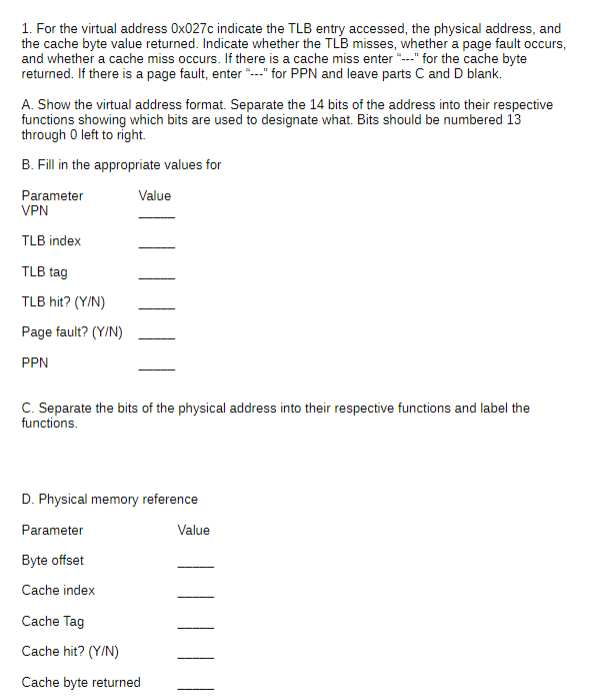

Use the memory system described below to answer the problems. The memory is byte addressable Memory accesses are to 1-byte words (not 4-byte words) Virtual addresses are 14 bits wide (n=14) Physical addresses are 12 bits wide (m12) The page size is 64 bytes (P=64) The TLB is 4-way set associate with 16 total entries The L1 d-cache is physically addresses and direct mapped, with a 4-byte line size and 16 total sets TI R 4 sets. 16 entries. 4-wav set associative. Page Table Only the first 16 PTEs are shown (If you are looking for something not in the first 16 entries assume it is a nade fault) see next page Cache 16 sets. 4 hute hlocks. direct manned 1. For the virtual address 0027c indicate the TLB entry accessed, the physical address, and the cache byte value returned. Indicate whether the TLB misses, whether a page fault occurs, and whether a cache miss occurs. If there is a cache miss enter "-." for the cache byte returned. If there is a page fault, enter " m." for PPN and leave parts C and D blank. A. Show the virtual address format. Separate the 14 bits of the address into their respective functions showing which bits are used to designate what. Bits should be numbered 13 through 0 left to right. B. Fill in the appropriate values for C. Separate the bits of the physical address into their respective functions and label the functions. D. Physical memory reference

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts