Question: Suppose that a processor has a datapath that is made up of modules with latencies of 2, 3, 4, 7, 3, 2 and 4 ns

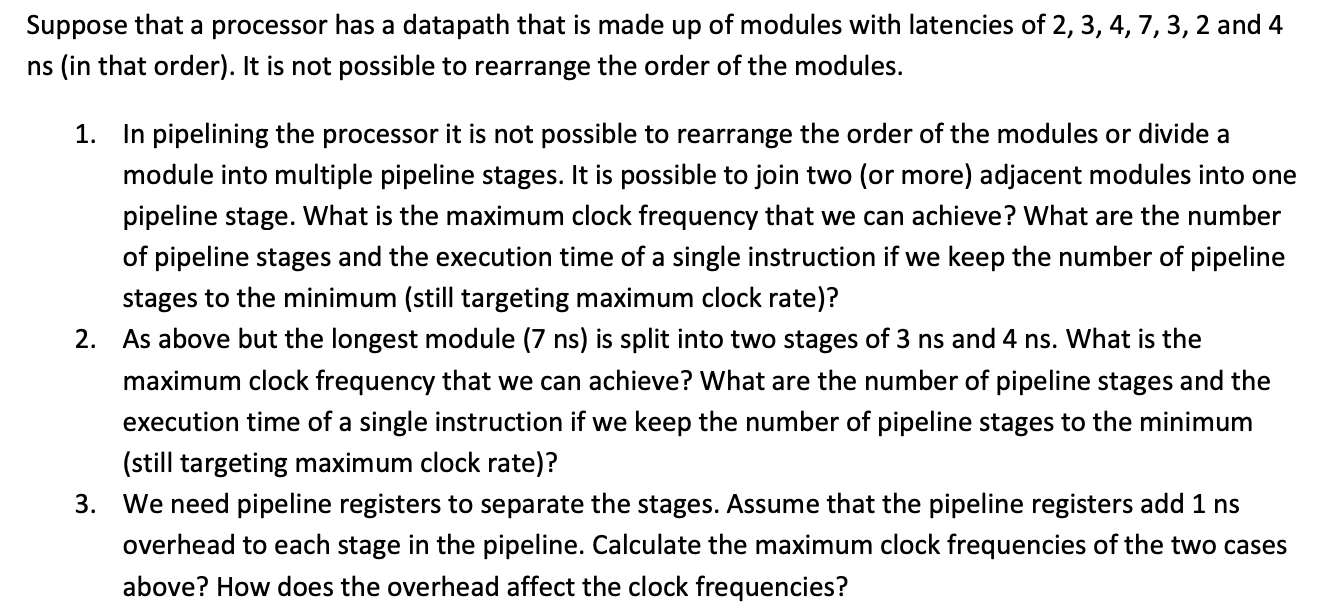

Suppose that a processor has a datapath that is made up of modules with latencies of 2, 3, 4, 7, 3, 2 and 4 ns (in that order). It is not possible to rearrange the order of the modules. 1. In pipelining the processor it is not possible to rearrange the order of the modules or divide a module into multiple pipeline stages. It is possible to join two (or more) adjacent modules into one pipeline stage. What is the maximum clock frequency that we can achieve? What are the number of pipeline stages and the execution time of a single instruction if we keep the number of pipeline stages to the minimum (still targeting maximum clock rate)? 2. As above but the longest module (7 ns) is split into two stages of 3 ns and 4 ns. What is the maximum clock frequency that we can achieve? What are the number of pipeline stages and the execution time of a single instruction if we keep the number of pipeline stages to the minimum (still targeting m num clock rate)? 3. We need pipeline registers to separate the stages. Assume that the pipeline registers add 1 ns overhead to each stage in the pipeline. Calculate the maximum clock frequencies of the two cases above? How does the overhead affect the clock frequencies

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts