Question: Suppose that the pipelined serial adder Figure 2 is reset in clock cycle 0. The least significant bits of four serial numbers N1, N2,

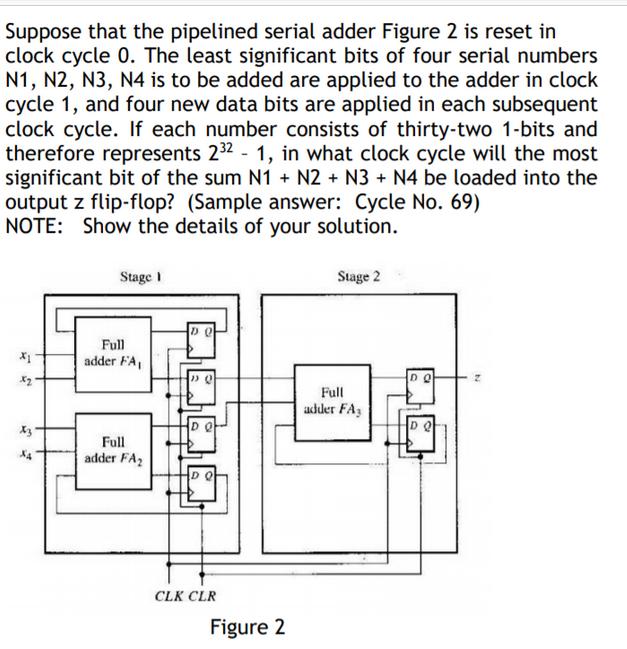

Suppose that the pipelined serial adder Figure 2 is reset in clock cycle 0. The least significant bits of four serial numbers N1, N2, N3, N4 is to be added are applied to the adder in clock cycle 1, and four new data bits are applied in each subsequent clock cycle. If each number consists of thirty-two 1-bits and therefore represents 22 - 1, in what clock cycle will the most significant bit of the sum N1 + N2 + N3 + N4 be loaded into the output z flip-flop? (Sample answer: Cycle No. 69) NOTE: Show the details of your solution. 2 W 44 Stage 1 Full adder FA Full adder FA ID Q DO CLK CLR Figure 2 Stage 2 Full adder FA

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts