Question: Suppose we have a cache memory with following properties: The memory is byte addressable. Memory accesses are to 1-byte words (not to 4-byte words). Addresses

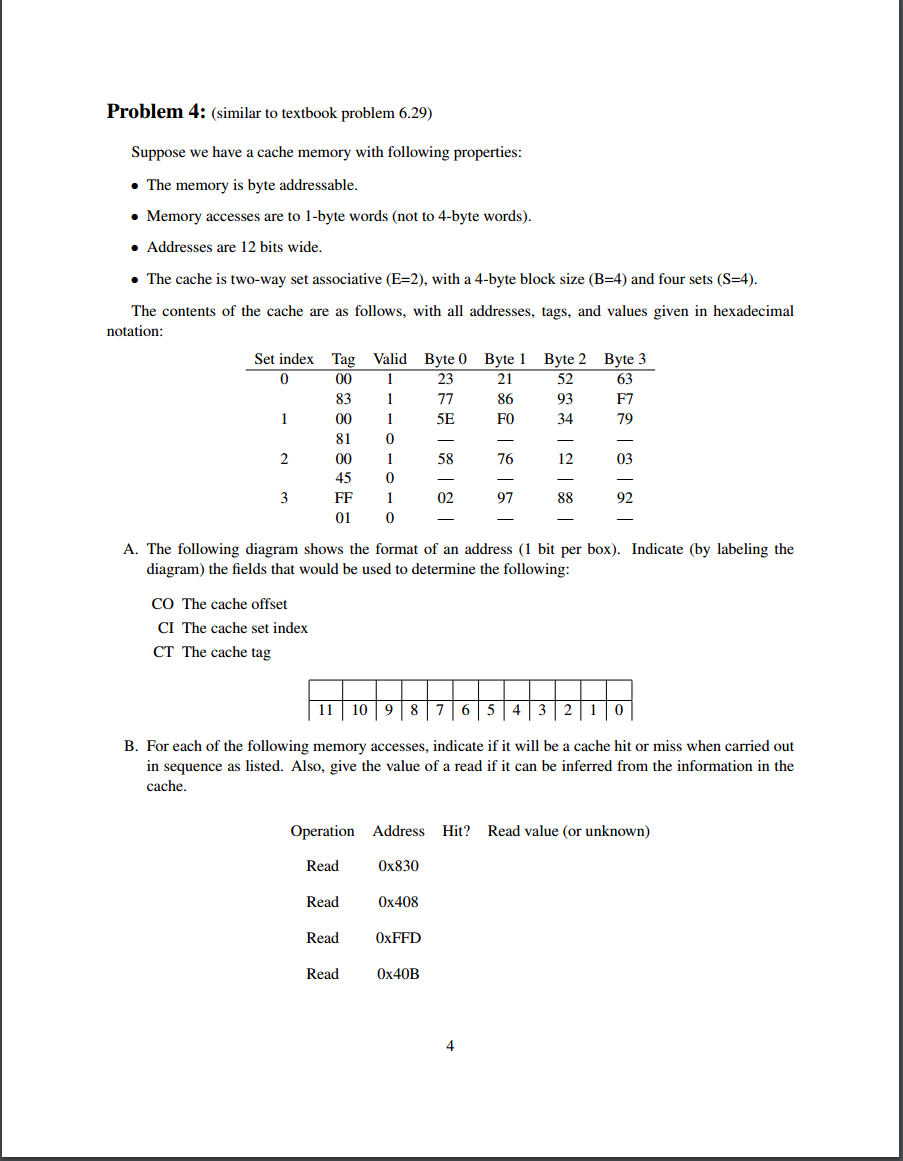

Suppose we have a cache memory with following properties: The memory is byte addressable. Memory accesses are to 1-byte words (not to 4-byte words). Addresses are 12 bits wide. The cache is two-way set associative (E=2), with a 4-byte block size (B=4) and four sets (S=4). The contents of the cache are as follows, with all addresses, tags, and values given in hexadecimal notation: A. The following diagram shows the format of an address (1 bit per box). Indicate (by labeling the diagram) the fields that would be used to determine the following: CO The cache offset CI The cache set index CT The cache tag B. For each of the following memory accesses, indicate if it will be a cache hit or miss when carried out in sequence as listed. Also, give the value of a read if it can be inferred from the information in the cache

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts