Question: Suppose you've designed a MIPS processor implementation in which the stages take the following lengths of time: IF = 20ns, ID = 10ns, EX=20 ns,

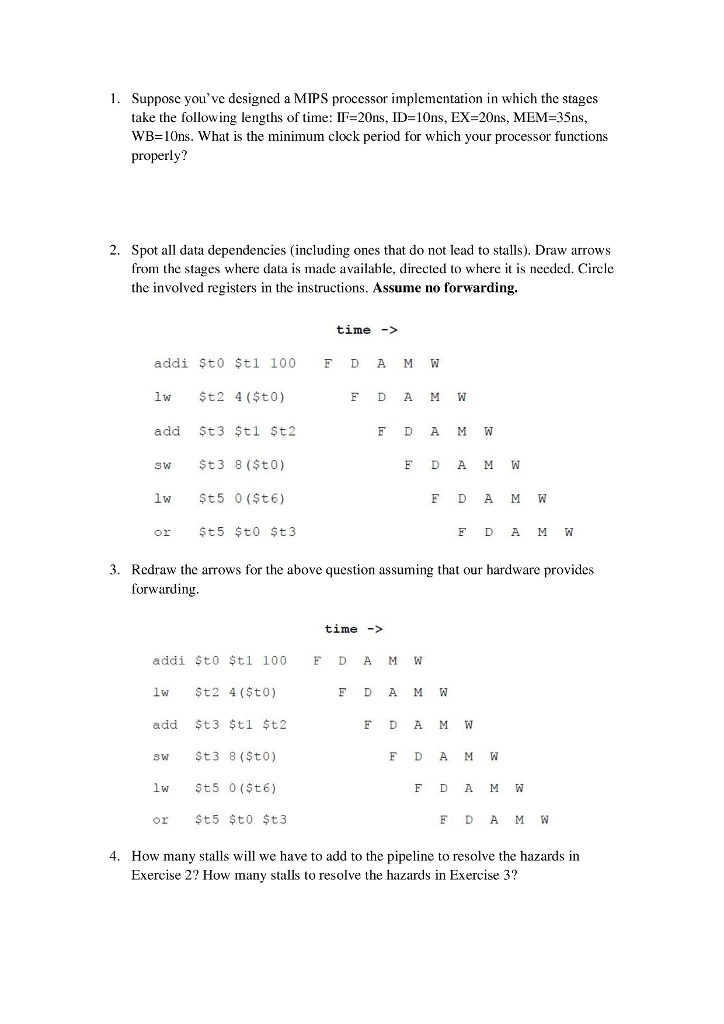

Suppose you've designed a MIPS processor implementation in which the stages take the following lengths of time: IF = 20ns, ID = 10ns, EX=20 ns, MEM = 35ns, WB-=0ns. What is the minimum clock period for which your processor functions properly? Spot all data dependencies (including ones that do not lead to stalls). Draw arrows from the stages where data is made available, directed to where it is needed. Circle the involved registers in the instructions. Assume no forwarding. addi $t0 $t1 100 F D A M W lw $t 2 4 ($to) F D A M W add $t3 $t1 $t2 FD A M W sw $t 3 8 ($to) F D A M W lw $t5 0 ($t6) F D A M W or $t5, $t0 $t3 F D A M W Redraw the arrows for the above question assuming that our hardware provides forwarding addi $to $t 1 100 F D A M W 1W $t2 4($t0) F D A M W add $t3 $t1 $t2 F D A M W SW $t3 8 ($t0) F D A M W lw $t5 0 ($ t6) F D A M W or $t5 $t0 $t3 F D A M W How many stalls will we have to add to the pipeline to resolve the hazards in Exercise 2? How many stalls to resolve the hazards in Exercise 3

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts