Question: SystemC/C++ Design and verify a communications interface Hi. I am having trouble with this problem. You must use SystemC to design it. The requirements of

SystemC/C++ Design and verify a communications interface

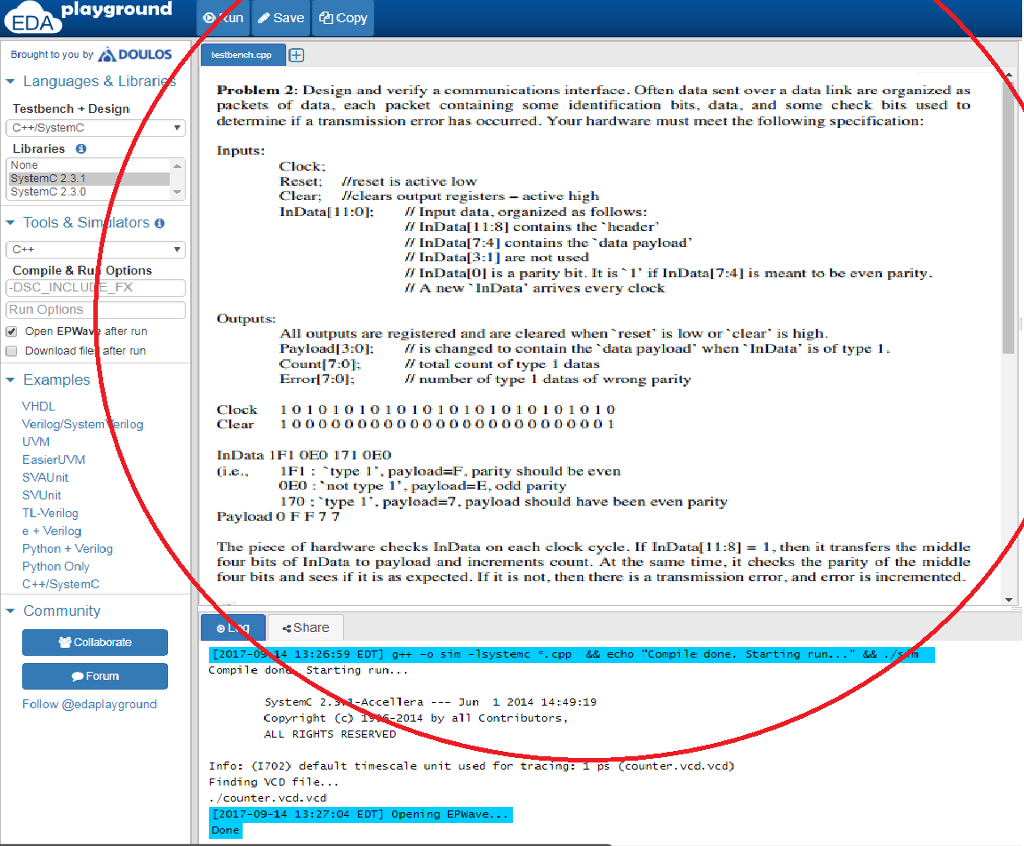

Hi. I am having trouble with this problem. You must use SystemC to design it. The requirements of the design are listed below under the Inputs and Outputs sections under Problem 2. You should also provide the design file (.cpp or .h files), test bench (.cpp), and picture of the simulation results.

You can use edaplayground (free) to run/simulate it

You can ignore the log section at the bottom of the picture. I was attempting a different problem earlier. Thanks!.

playground EDA 0'un ., Save Copy Brought to you by DOULOS Languages & Libran Problem 2: Design and verify a communications interface. Often data sent over a data link are organized as packets of data each packet containing some identification bits data and some check bits used to determine if a transmission error has occurred. Your hardware must meet the following specification Testbench Design C++/SystemC Libraries E None SystemC 2.3.1 Inputs: Clock Reset: reset is active low Clear; Jclears output registers-active high InDatal 1 1:0]: SystemC 2.3.0 f Input data, organized as follows: Tools &S torso InDatal 11:8] contains the header InDatal7:41 contains the data payload InDatal:1 are not used Compile & Ru Options -DSC INCLUIE FX Run Options // InDatalol is a parity bit. It isl, if InDatal 7:4] is meant to be even parity A new InData arrives every clock ts. Open EPWave after run All outputs are registered and are cleared when reset' is low or "clear, is high Payload|3:01 Count 7:0 Errorl7:0 Download fileafter run // is changed to contain the-data payload' when-InData, is of type 1. total count of type 1 datas number of type 1 datas of wrong parity Examples VHDL Verilog/System erilog UVM EasierUVM SVAUnit SVUnit TL-Verilog e Verilog Python + Verilag Python Only C++/SystemC Clock Clear 101010 10 10101 0101010 10 1 0 1 0 1 0 0000000 000 0 0 00 000 0 00 0001 InData 1F1 OHO 171 OEO i F1: ~ type 1 . payload=F, parity should be even not type 1' payload-E. odd parity 170 :type 1 . payload-7. payload should have been even parity PayloadOFF77 The piece of hardware checks InData on each clock cycle. If InDatal 11:8].then it transfers the middle four bits of InData to payload and inerements count. At the same time, it checks the parity of the middle four bits and sees if it is as expected. If it is not, then there is a transmission error, and error is incremented. Community Share em one ar un Compile do Starting run.. Systemc 2 Copyright (c) ALL RIGHTS RESERVED Accellera ---Jun 1 2014 14:49:19 2014 by all Contributors, Follow @edaplayground Info: (I702) default timescale unit used for tracing: i ps Ccounter.vcd. vcd) Finding VCD file. .. /counter.vcd.vcd ni n ave

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts