Question: Take this verilog syntax and write the Vhdl syntax that would correspond module count enabler (input reset,clk,output reg en_out); parameter buswidth-16, full count-1771: // default

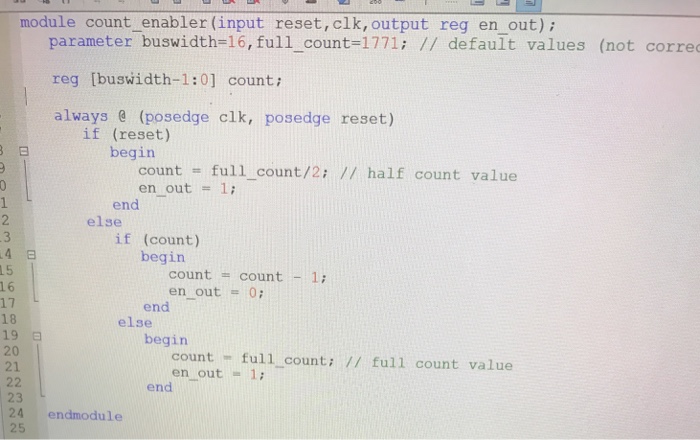

module count enabler (input reset,clk,output reg en_out); parameter buswidth-16, full count-1771: // default values (not corre reg [buswidth-1:0] count: always e (posedge clk, posedge reset) if (reset) begin count = full. Count/2; // half count value en out 1; end else if (count) :4 15 16 17 L 18 19 20 21 begin count count - 1; enout 0; - end else begin count full count: / full count value enout = 1 ; - end 23 24 endmodule 25

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts