Question: The aim of this task is to implement a Carry - Lookahead Adder ( CLA ) in SystemVerilog. The CLA is to add two n

The aim of this task is to implement a CarryLookahead Adder CLA in SystemVerilog. The CLA is to add two n bit numbers together. It consists of blocks for k columns each so that n k

Except for the testbench, it is not allowed to use addition operators, comparison operators or similar, use only operators from Boolean algebra Boolean reduction operators are allowed

Note: You can also receive points for later parts of the task if you were unable to solve previous parts.

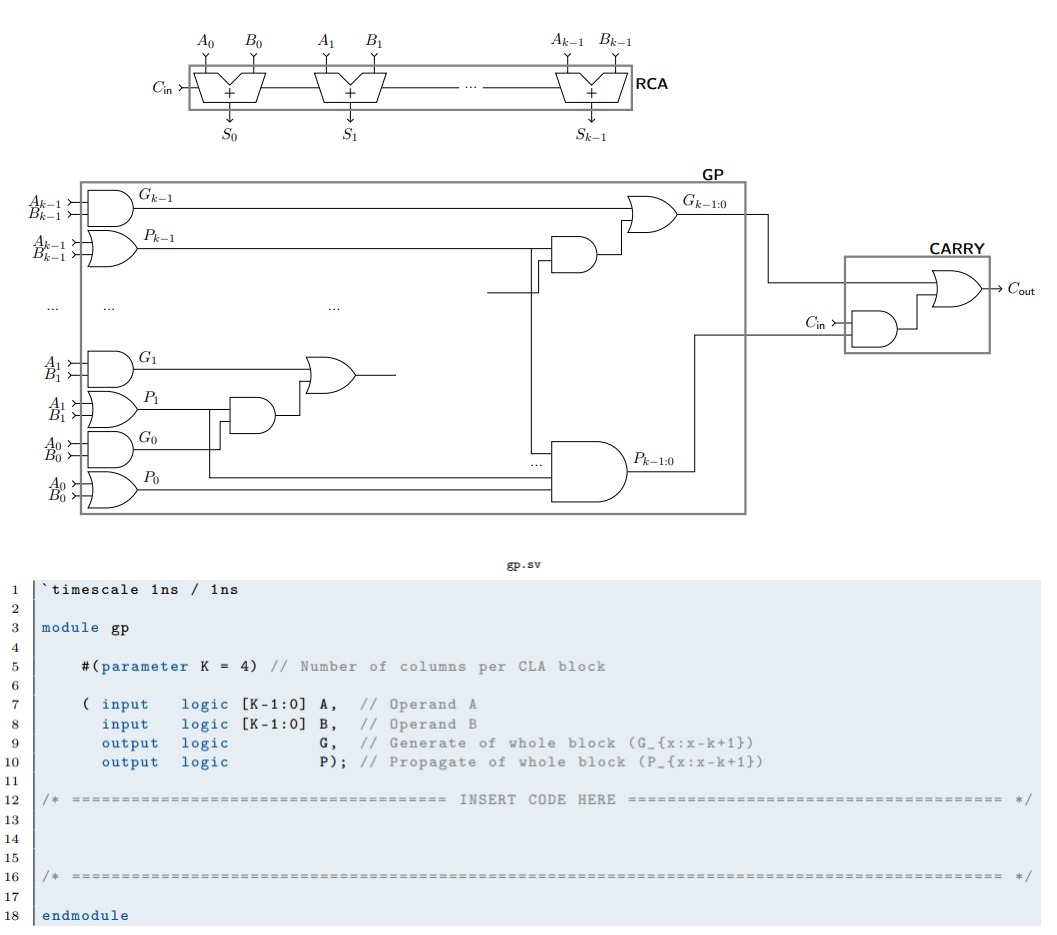

A CLA block for k columns is constructed as follows from the blocks RCA, GP and CARRY:

Implement the parameterized SystemVerilog module gp which implements the GP block of a kcolumn CLA block.

Note: Among other things, a generate block is required to calculate the output G The task can be solved by using the module carry in the generate block. To do this, try replacing parts of the GP circuit with CARRY.

Note: You can compile and test your code with the following command:

Windows: simbat gp Otherwise: simsh gp

Note: If you do not solve this task, you can use gpfiller.sv as an implementation of gp for the following tasks. implementation of gp for the following tasks. To do this, copy it to gpsv This implementation is correct, but uses addition operators and comparisons internally and is therefore not a valid solution for this subtask.'timescale ns ns

module gp

#parameter Number of columns per CLA block

input logic : Operand

input logic : Operand

output logic G Generate of whole block G:

output logic P; Propagate of whole block Px:xk

P

endmodule

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock