Question: The Intel 8086 microprocessor was introduced in 1978. It had an initial clock frequency of 5 MHz, had 29,000 transistors, made with 3 um technology,

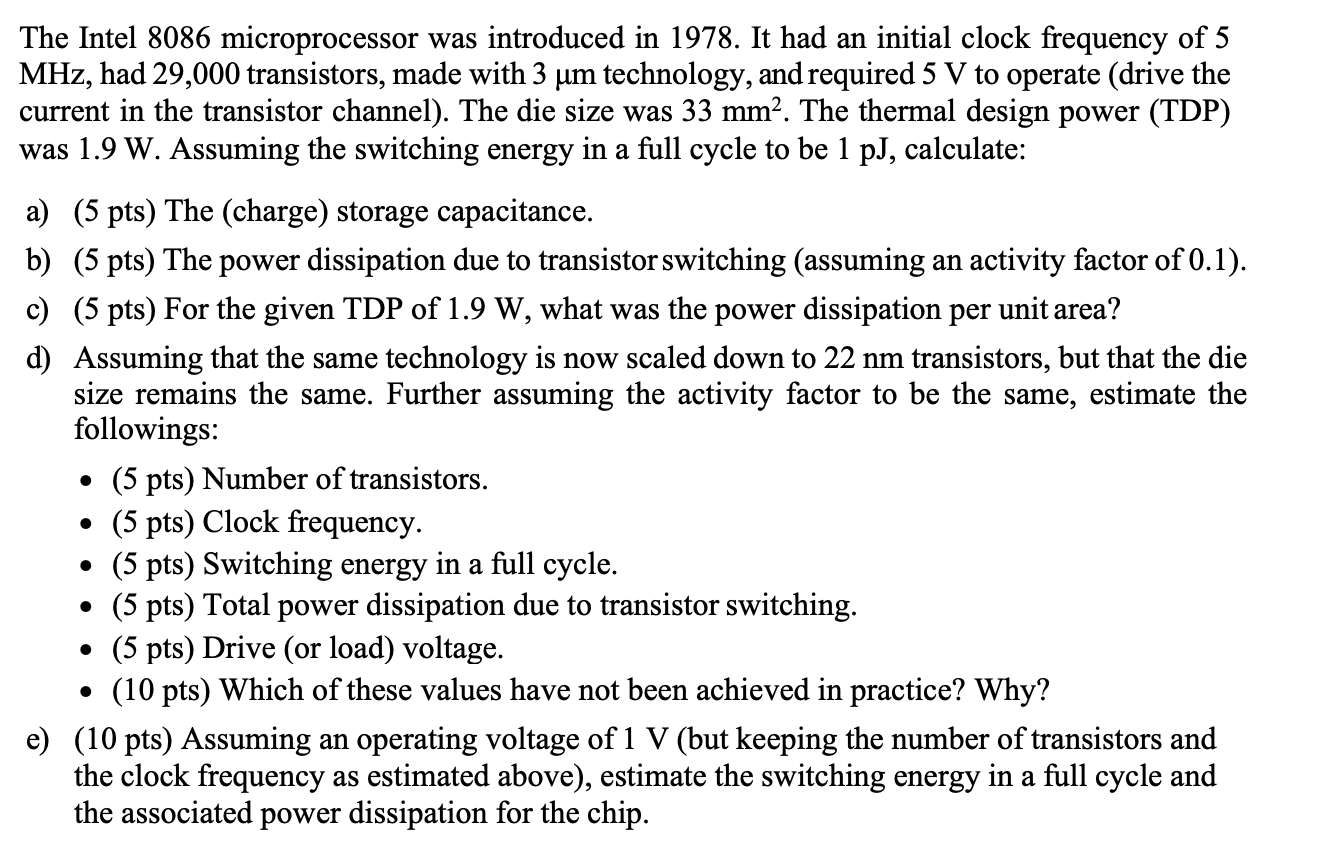

The Intel 8086 microprocessor was introduced in 1978. It had an initial clock frequency of 5 MHz, had 29,000 transistors, made with 3 um technology, and required 5 V to operate (drive the current in the transistor channel). The die size was 33 mm2. The thermal design power (TDP) was 1.9 W. Assuming the switching energy in a full cycle to be 1 pJ, calculate: a) (5 pts) The (charge) storage capacitance. b) (5 pts) The power dissipation due to transistor switching (assuming an activity factor of 0.1). c) (5 pts) For the given TDP of 1.9 W, what was the power dissipation per unit area? d) Assuming that the same technology is now scaled down to 22 nm transistors, but that the die size remains the same. Further assuming the activity factor to be the same, estimate the followings: (5 pts) Number of transistors. (5 pts) Clock frequency. (5 pts) Switching energy in a full cycle. (5 pts) Total power dissipation due to transistor switching. (5 pts) Drive (or load) voltage. (10 pts) Which of these values have not been achieved in practice? Why? e) (10 pts) Assuming an operating voltage of 1 V (but keeping the number of transistors and the clock frequency as estimated above), estimate the switching energy in a full cycle and the associated power dissipation for the chip. The Intel 8086 microprocessor was introduced in 1978. It had an initial clock frequency of 5 MHz, had 29,000 transistors, made with 3 um technology, and required 5 V to operate (drive the current in the transistor channel). The die size was 33 mm2. The thermal design power (TDP) was 1.9 W. Assuming the switching energy in a full cycle to be 1 pJ, calculate: a) (5 pts) The (charge) storage capacitance. b) (5 pts) The power dissipation due to transistor switching (assuming an activity factor of 0.1). c) (5 pts) For the given TDP of 1.9 W, what was the power dissipation per unit area? d) Assuming that the same technology is now scaled down to 22 nm transistors, but that the die size remains the same. Further assuming the activity factor to be the same, estimate the followings: (5 pts) Number of transistors. (5 pts) Clock frequency. (5 pts) Switching energy in a full cycle. (5 pts) Total power dissipation due to transistor switching. (5 pts) Drive (or load) voltage. (10 pts) Which of these values have not been achieved in practice? Why? e) (10 pts) Assuming an operating voltage of 1 V (but keeping the number of transistors and the clock frequency as estimated above), estimate the switching energy in a full cycle and the associated power dissipation for the chip

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts