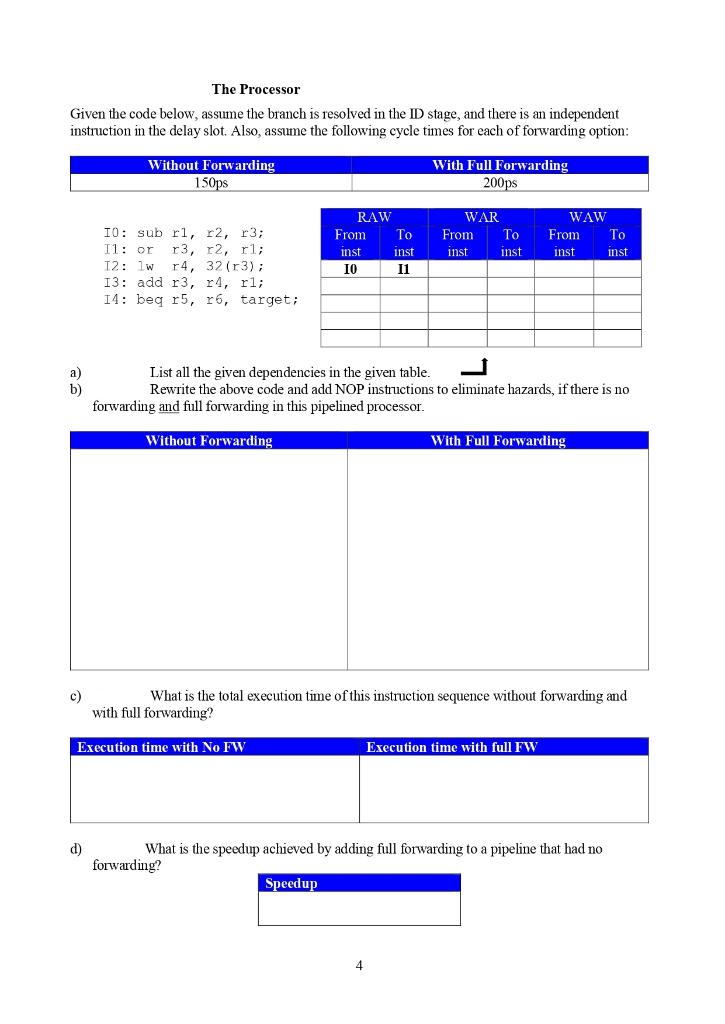

Question: The Processor Given the code below, assume the branch is resolved in the ID stage, and there is an independent instruction in the delay slot.

The Processor Given the code below, assume the branch is resolved in the ID stage, and there is an independent instruction in the delay slot. Also, assume the following cycle times for each of forwarding option: Without Forwarding 150ps With Full Forwarding 200ps WAR From inst inst RAW From To inst inst IO 11 WAW From To inst inst 11: or 10: sub ri, r2, r3; r3, r2, r1; 12: lw r4, 32 (r3); 13: add r3, r4, rl; 14: beq r5, r6, target; a) b) List all the given dependencies in the given table. Rewrite the above code and add NOP instructions to eliminate hazards, if there is no forwarding and full forwarding in this pipelined processor Without Forwarding With Full Forwarding c) What is the total execution time of this instruction sequence without forwarding and with full forwarding? Execution time with No FW Execution time with full FW d) What is the speedup achieved by adding full forwarding to a pipeline that had no forwarding? Speedup 4

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts