Question: The tables below represent an 8-line, 2-way associative cache, a 4-line, 2-way associative cache, and a 4-line, fully associative cache. (Fully associative means that all

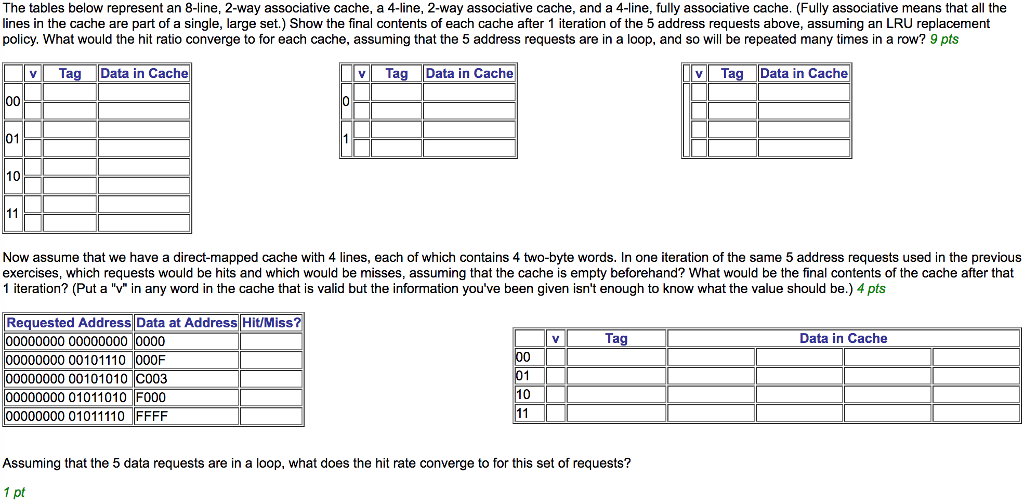

The tables below represent an 8-line, 2-way associative cache, a 4-line, 2-way associative cache, and a 4-line, fully associative cache. (Fully associative means that all the lines in the cache are part of a single, large set.) Show the final contents of each cache after 1 iteration of the 5 address requests above, assuming an LRU replacement policy. What would the hit ratio converge to for each cache, assuming that the 5 address requests are in a loop, and so will be repeated many times in a row? Now assume that we have a direct-mapped cache with 4 lines, each of which contains 4 two-byte words. In one iteration of the same 5 address requests used in the previous exercises, which requests would be hits and which would be misses, assuming that the cache is empty beforehand? What would be the final contents of the cache after that 1 iteration? (Put a "v" in any word in the cache that is valid but the information you've been given isn't enough to know what the value should be.) Assuming that the 5 data requests are in a loop, what does the hit rate converge to for this set of requests

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts