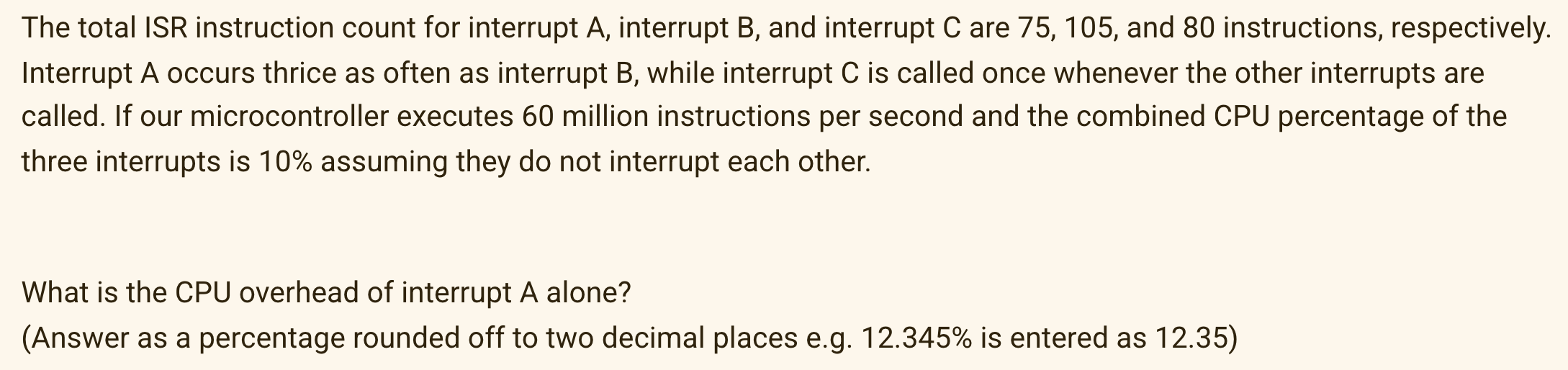

Question: The total ISR instruction count for interrupt A, interrupt B, and interrupt C are 75, 105, and 80 instructions, respectively. Interrupt A occurs thrice as

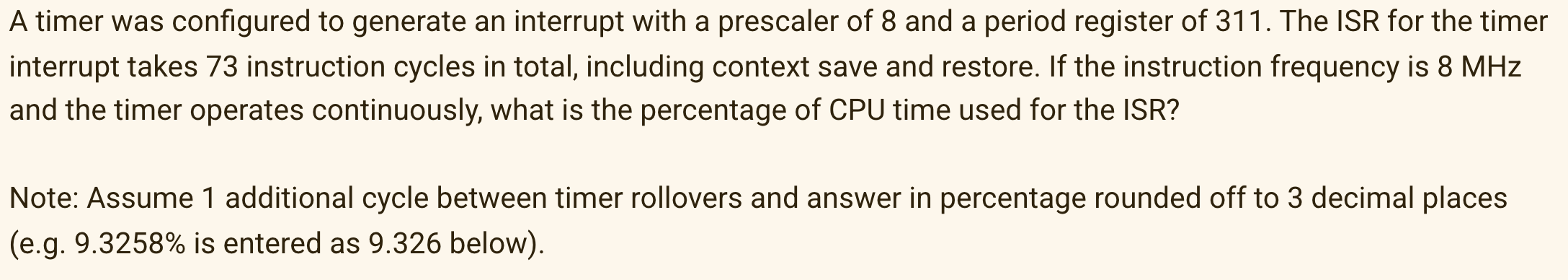

The total ISR instruction count for interrupt A, interrupt B, and interrupt C are 75, 105, and 80 instructions, respectively. Interrupt A occurs thrice as often as interrupt B, while interrupt C is called once whenever the other interrupts are called. If our microcontroller executes 60 million instructions per second and the combined CPU percentage of the three interrupts is 10% assuming they do not interrupt each other. What is the CPU overhead of interrupt A alone? (Answer as a percentage rounded off to two decimal places e.g. 12.345% is entered as 12.35) A timer was configured to generate an interrupt with a prescaler of 8 and a period register of 311. The ISR for the timer a interrupt takes 73 instruction cycles in total, including context save and restore. If the instruction frequency is 8 MHz and the timer operates continuously, what is the percentage of CPU time used for the ISR? Note: Assume 1 additional cycle between timer rollovers and answer in percentage rounded off to 3 decimal places (e.g. 9.3258% is entered as 9.326 below)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts