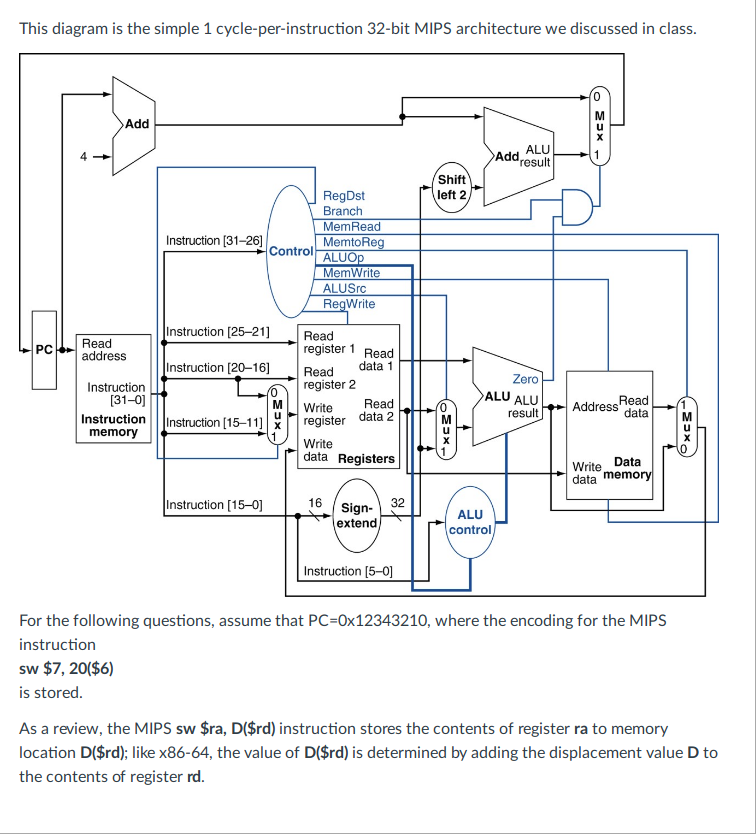

Question: This diagram is the simple 1 cycle-per-instruction 32-bit MIPS architecture we discussed in class. 0 MI Add ALU Add result 4 Shift left 2 RegDst

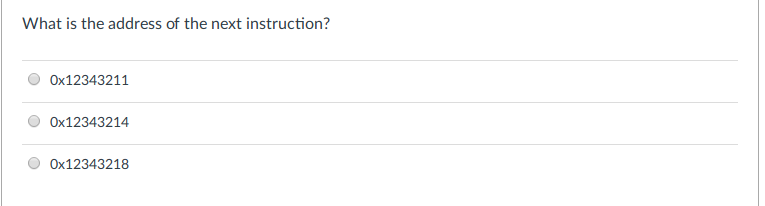

This diagram is the simple 1 cycle-per-instruction 32-bit MIPS architecture we discussed in class. 0 MI Add ALU Add result 4 Shift left 2 RegDst Branch MemRead MemtoRe Instruction[31-2? Control ALU MemWrite ALUSrc RegWrite Instruction [25-21] Read register 1 Read Read PCaddress Instruction [20-16 Read data 1 Zero ALU ALU result register 2 Read Address data Instruction uWrite Read 1Write [31-0) InstructionInstruction [15egister data2 memory data Registers Data Write data memo Instruction [15-0] 16 Sign- 32 ALU control extend Instruction [5-0 For the following questions, assume that PC-0x12343210, where the encoding for the MIPS instruction sw $7, 20($6) is stored As a review, the MIPS sw $ra, D($rd) instruction stores the contents of register ra to memory location D($rd); like x86-64, the value of D($rd) is determined by adding the displacement value D to the contents of register rd

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts