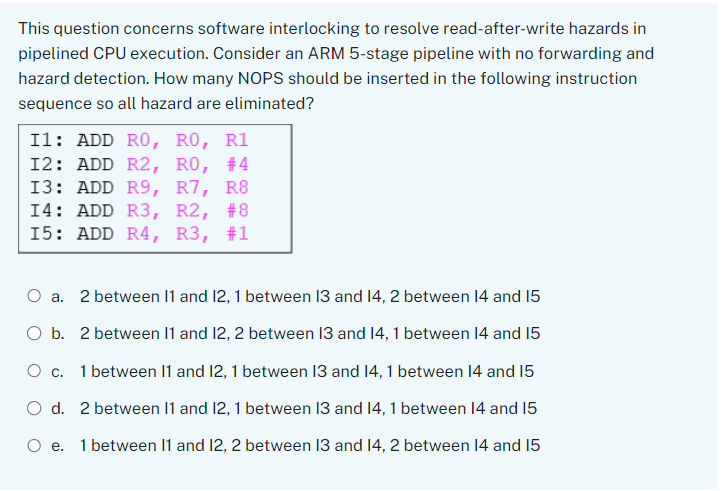

Question: This question concerns software interlocking to resolve read - after - write hazards in pipelined CPU execution. Consider an ARM 5 - stage pipeline with

This question concerns software interlocking to resolve readafterwrite hazards in

pipelined CPU execution. Consider an ARM stage pipeline with no forwarding and

hazard detection. How many NOPS should be inserted in the following instruction

sequence so all hazard are eliminated?

a between I and I, between and between I and

b between I and I, between and between and

c between and I, between and between and

d between and I, between I and I between I and I

e between I and between and between and

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock