Question: Use the following defined hypothetical machine architecture, which is the same as from our textbook, but with some additional opcodes. Opcode (binary) Mnemonic Description 0001

Use the following defined hypothetical machine architecture, which is the same as from our textbook, but with some additional opcodes.

| Opcode (binary) | Mnemonic | Description |

| 0001 | LOAD | Load AC from memory (memory -> AC) |

| 0010 | STOR | Store AC to memory (AC -> memory) |

| 0011 | MUL | Multiply AC and memory (AC * memory -> AC) |

| 0100 | SUB | Subtract memory from AC (AC - memory -> AC) |

| 0101 | ADD | Add to AC from memory (AC + memory -> AC) |

| 0110 | JMP | Jump to address (absolute jump) |

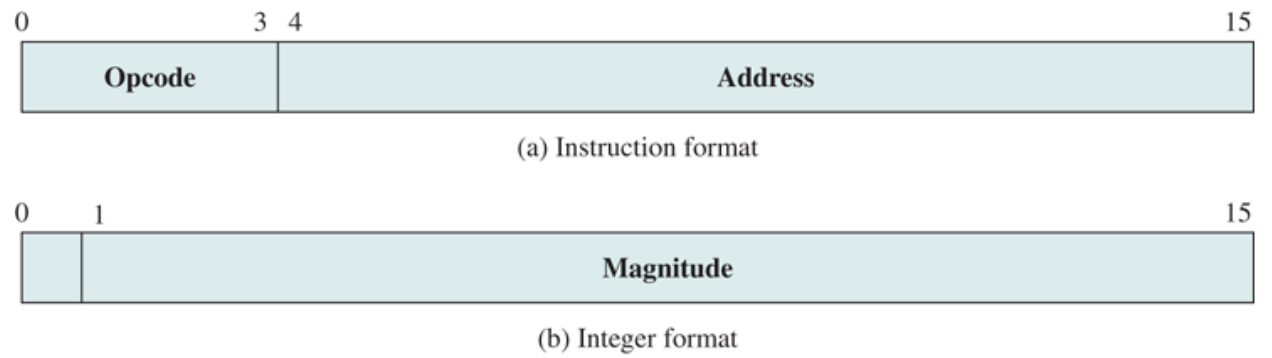

Don't forget that our hypothetical machine uses 16 bit words, and the following are the instruction format and integer format of the machine.

The integer format uses a simple signed-magnitude format, with a single sign bit that indicates a positive or negative integer integer value.

Given the following initial state of memory, show the first 8 fetch/execute cycles of this hypothetical machine. ?All values in the registers and memory should be given as hexadecimal values. ?You should show the state of memory and registers for both the fetch and execute steps of the first 4 cycles of the hypothetical machine execution.

| Address | Memory | CPU registers | |

| 300 | 2940 | 0300 | PC |

| 301 | 3941 | 800B | AC |

| 302 | 2941 | IR | |

| 303 | 6400 | ||

| 940 | 0100 | ||

| 941 | 8001 |

0 0 Opcode 1 34 Address (a) Instruction format Magnitude (b) Integer format 15 15

Step by Step Solution

3.50 Rating (150 Votes )

There are 3 Steps involved in it

program ANSWER execution as peur figure 35 from textbook Inst... View full answer

Get step-by-step solutions from verified subject matter experts