Question: 5. Memory hierarchy: Cache design and analysis (13 points) The memory is byte addressable. Memory accesses are to 1-byte words. Physical addresses are 8 bits

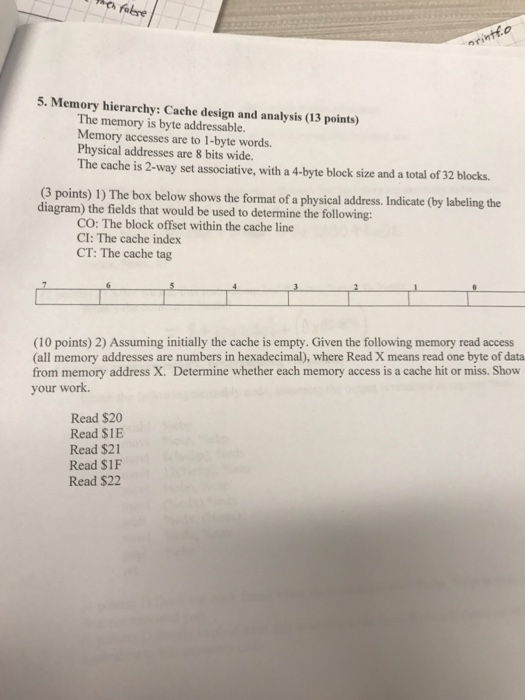

5. Memory hierarchy: Cache design and analysis (13 points) The memory is byte addressable. Memory accesses are to 1-byte words. Physical addresses are 8 bits wide. The cache is 2-way set associative, with a 4-byte block size and a total of 32 blocks. (3 points) 1) The box below shows the format of a physical address. Indicate (by labeling the diagram) the fields that would be used to determine the following: CO: The block offset within the cache line CI: The cache index CT: The cache tag (10 points) 2) Assuming initially the cache is empty. Given the following memory read access (all memory addresses are numbers in hexadecimal), where Read X means read one byte of data from memory address X. Determine whether each memory access is a cache hit or miss. Show your work Read $20 Read S1E Read $21 Read S1F Read $22

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts