Question: using the given code, complete part 4 by coding a VHDL file, not necessary to show the confirmation on a DE10-Lite Board. Part III's code:

using the given code, complete part 4 by coding a VHDL file, not necessary to show the confirmation on a DE10-Lite Board.

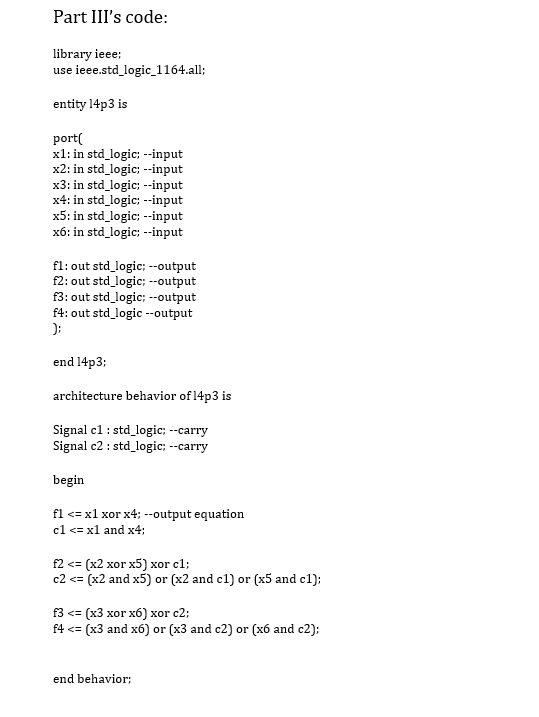

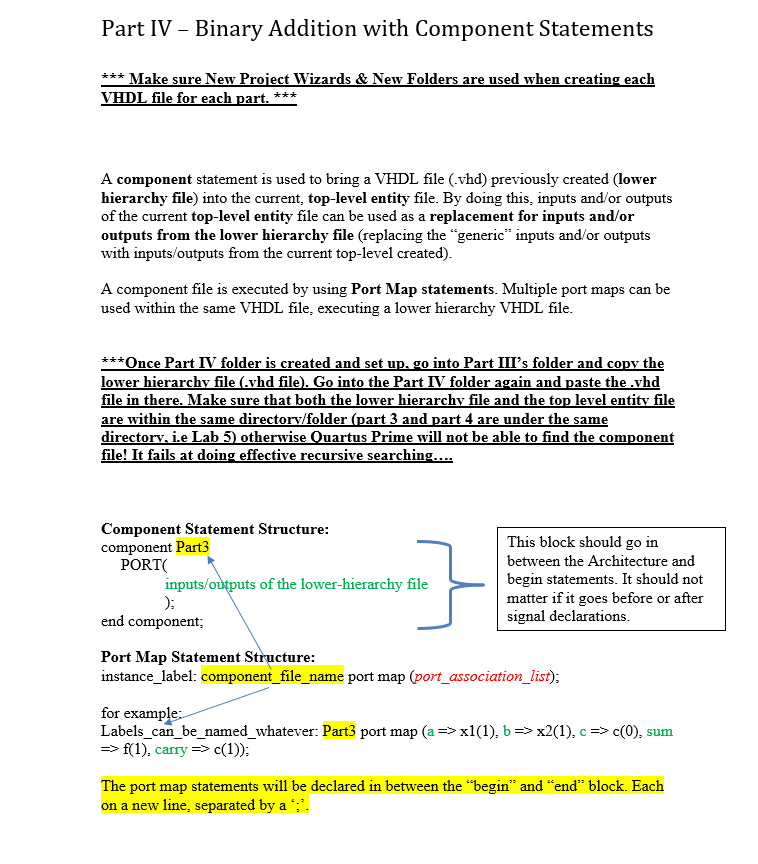

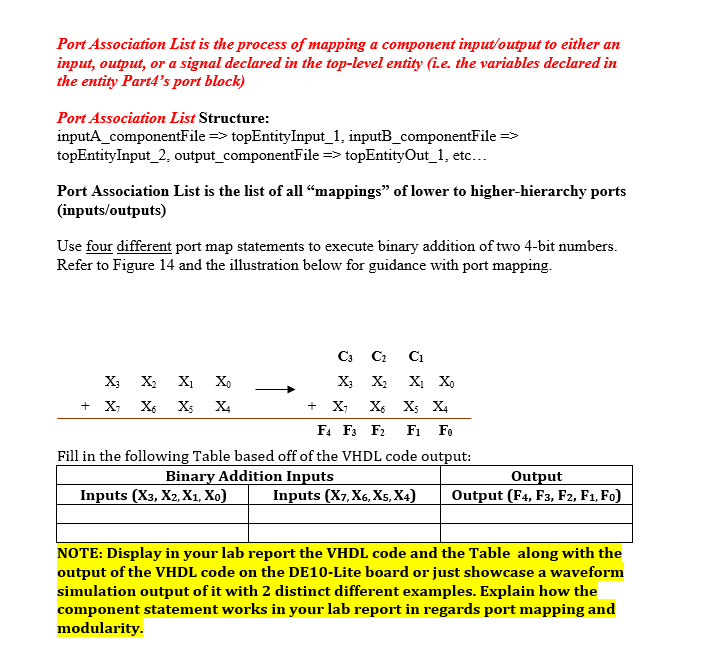

Part III's code: library ieee; use ieee.std_logic_1164.all; entity 14p3 is port xl: in std_logic; --input x2: in std_logic; --input x3: in std_logic; --input x4: in std_logic; --input x5: in std_logic; --input x6: in std_logic; --input fl: out std_logic: --output f2: out std_logic; --output f3: out std_logic; --output f4: out std_logic --output ); end 14p3: architecture behavior of 14p3 is Signal c1 : std_logic; --carry Signal c2 : std_logic; --carry begin fl x1(1), b => x2(1), c => c(0), sum => f(1), carry => c(1)); The port map statements will be declared in between the "begin" and "end" block. Each on a new line, separated by a ";'. Port Association List is the process of mapping a component input/output to either an input, output, or a signal declared in the top-level entity (i.e. the variables declared in the entity Part4's port block) Port Association List Structure: inputA_componentFile => topEntityInput_1, inputB_componentFile => topEntityInput_2, output_componentFile => topEntityOut_1, etc... Port Association List is the list of all mappings" of lower to higher-hierarchy ports (inputs/outputs) Use four different port map statements to execute binary addition of two 4-bit numbers. Refer to Figure 14 and the illustration below for guidance with port mapping. . . . X; X2 Xi X X; X X X + X X X X + X X4 X5 X6 F4 F3 F2 Fi Fo Fill in the following Table based off of the VHDL code output: Binary Addition Inputs Output Inputs (X3, X2, X1, Xo) Inputs (X7, X6, X5, X4) Output (F4, F3, F2, F1, F0) NOTE: Display in your lab report the VHDL code and the Table along with the output of the VHDL code on the DE10-Lite board or just showcase a waveform simulation output of it with 2 distinct different examples. Explain how the component statement works in your lab report in regards port mapping and modularity

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts