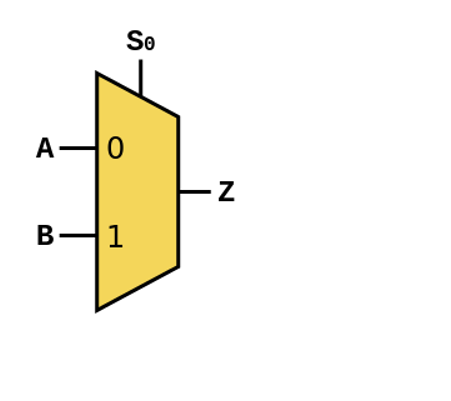

Question: Using VHDL code, implement a 2-to-1 multiplexer. A 2^n -to-1MUX has 2^n inputs with n selectors. the 2-to-1 multiplexer outputs the input signal A when

Using VHDL code, implement a 2-to-1 multiplexer. A 2^n -to-1MUX has 2^n inputs with n selectors. the 2-to-1 multiplexer outputs the input signal A when the selector signal S is equal to 0 otherwise it outputs the input signal B. You need to implement 2 styles, one behavioral and one structural. The structural model uses only NOT, OR and AND gates. It realizes its Boolean function which only uses NOT, OR and AND gates. Use the following:

Using VHDL code, implement a 2-to-1 multiplexer. A 2^n -to-1MUX has 2^n inputs with n selectors. the 2-to-1 multiplexer outputs the input signal A when the selector signal S is equal to 0 otherwise it outputs the input signal B. You need to implement 2 styles, one behavioral and one structural. The structural model uses only NOT, OR and AND gates. It realizes its Boolean function which only uses NOT, OR and AND gates. Use the following:

Library IEEE;

use IEEE.STD_LOGIC_ 1164.ALL;

use IEEE.NUMERCI_STD.ALL;

entity MUX_structural is

Port(A : in std_logic;

B : in std_logic;

S : in std_logic;

Z : out std_logic);

end MUX_structural;

In the behavioral description, describe the behavior of your target circuit and the synthesis tool creates a gate-level layout of your design. Use a single VHDL select assignment only. Use the following.

Library IEEE;

use IEEE.STD_LOGIC_ 1164.ALL;

use IEEE.NUMERCI_STD.ALL;

entity MUX_behavioral is

Port(A : in std_logic;

B : in std_logic;

S : in std_logic;

Z : out std_logic);

end MUX_behavioral;

Once completed, Write a testbench code and Show representative simulation plots of the 2-to-1 MUX circuits for all the possible input values.

So AGO -Z B H1

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts