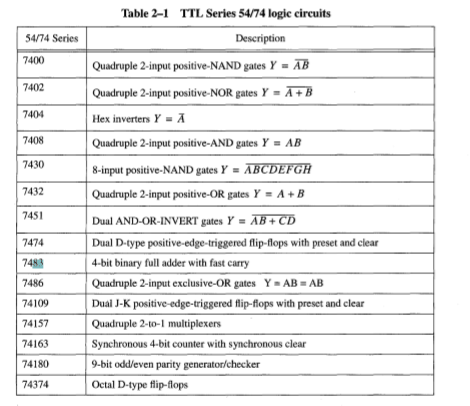

Question: Using VHDL write an entity and architecture pair for each of the TTL devices in Table 2-1. Table 2-1 TTL Series 54/74 logic circuits 54/74

Using VHDL write an entity and architecture pair for each of the TTL devices in Table 2-1.

Table 2-1 TTL Series 54/74 logic circuits 54/74 Series 7400 7402 7404 7408 7430 7432 451 7474 7483 7486 74109 74157 74163 74180 74374 Quadruple 2-input positive-NAND gates Y- Quadruple 2-input positive-NOR gates )-A+ Hex inverters Y A Quadruple 2-input positive-AND gates Y = AB 8-input positive-NAND gates Y ABCDEFGH Quadruple 2-input positive-OR gates Y A+B Dual AND-OR-INVERT gates = AB + CD Dual D-type positive-edge-triggered flip-flops with preset and clear 4-bit binary full adder with fast carry Quadruple 2-input exclusive-OR gates YAB AB Dual J-K positive-edge-triggered flip-lops with preset and clear Quadruple 2-to-1 multiplexers Synchronous 4-bit counter with synchronous clear 9-bit odd/even parity Octal D-type flip-flops Table 2-1 TTL Series 54/74 logic circuits 54/74 Series 7400 7402 7404 7408 7430 7432 451 7474 7483 7486 74109 74157 74163 74180 74374 Quadruple 2-input positive-NAND gates Y- Quadruple 2-input positive-NOR gates )-A+ Hex inverters Y A Quadruple 2-input positive-AND gates Y = AB 8-input positive-NAND gates Y ABCDEFGH Quadruple 2-input positive-OR gates Y A+B Dual AND-OR-INVERT gates = AB + CD Dual D-type positive-edge-triggered flip-flops with preset and clear 4-bit binary full adder with fast carry Quadruple 2-input exclusive-OR gates YAB AB Dual J-K positive-edge-triggered flip-lops with preset and clear Quadruple 2-to-1 multiplexers Synchronous 4-bit counter with synchronous clear 9-bit odd/even parity Octal D-type flip-flops

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts