Question: Verilog code and flow chart You are required to design and implement a multiplier unit that can perform multiplication on two 4-bit binary numbers using

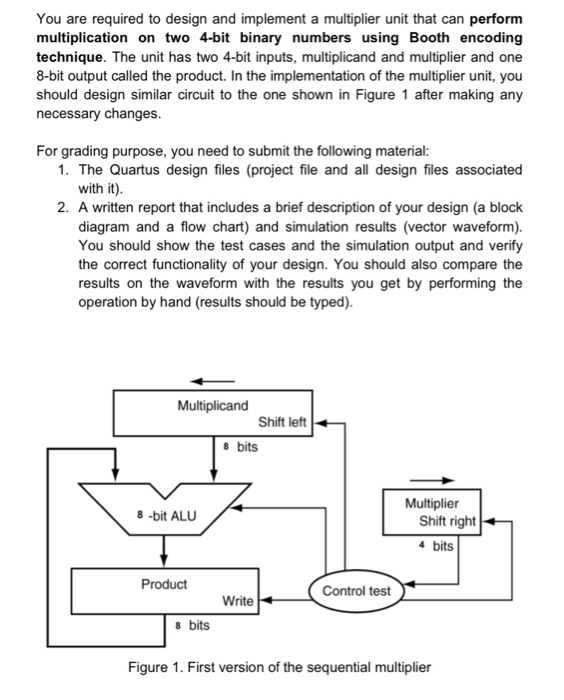

You are required to design and implement a multiplier unit that can perform multiplication on two 4-bit binary numbers using Booth encoding technique. The unit has two 4-bit inputs, multiplicand and multiplier and one 8-bit output called the product. In the implementation of the multiplier unit, you should design similar circuit to the one shown in Figure 1 after making any necessary changes For grading purpose, you need to submit the following material: 1. The Quartus design files (project file and all design files associated with it) 2. A written report that includes a brief description of your design (a block diagram and a flow chart) and simulation results (vector waveform). You should show the test cases and the simulation output and verify the correct functionality of your design. You should also compare the results on the waveform with the results you get by performing the operation by hand (results should be typed) Multiplicand Shift left s bits Multiplier 8-bit ALU Shift right 4 bits Product Control test Write s bits Figure 1. First version of the sequential multiplier

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts