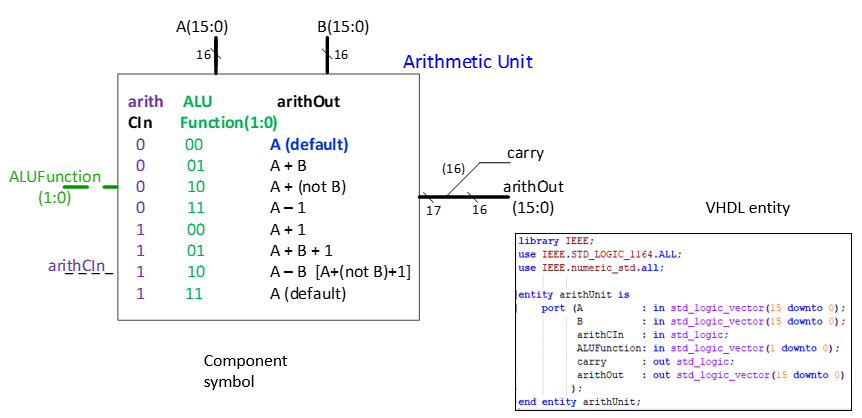

Question: VHDL - Arithmetic Unit (arithUnit) vhdl code for arithmetic unit A(15:0) B(15:0) 16 16 Arithmetic Unit arith ALU CIn Function(1:0) arithOut 0 0 A (default)

VHDL - Arithmetic Unit (arithUnit)

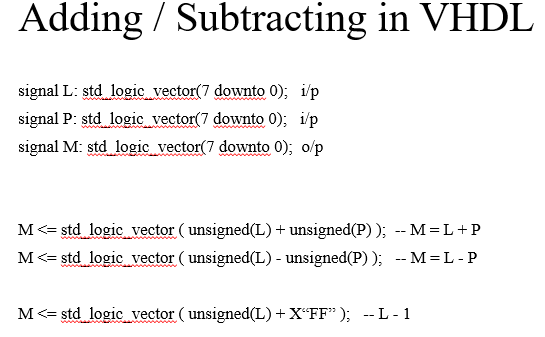

vhdl code for arithmetic unit

![B)+1] A (default) 01 10 library IEEE: use IEEE. STD LOGIC 1164.ALL](https://dsd5zvtm8ll6.cloudfront.net/si.experts.images/questions/2024/10/6703fe36ea718_9346703fe3690563.jpg)

A(15:0) B(15:0) 16 16 Arithmetic Unit arith ALU CIn Function(1:0) arithOut 0 0 A (default) A + B A + (not B) carry 01 10 ALUFunction arithOut 0 16 (15:0) VHDL entity 17 A+1 A +B+1 A-B [A+(not B)+1] A (default) 01 10 library IEEE: use IEEE. STD LOGIC 1164.ALL use IEEE.nuneric std.all: arithCln 1 entity arithUnit is : in std logic vector (15 downto 0) : in std_logic_vector (15 downto 0) port (A arithCIn: in std logic; ALUFunction: in std logic vector (1 dowmto 0) Component symbol : out std_logic : out std logic_vector (15 downto 0) arithout end entity arithUnit; A(15:0) B(15:0) 16 16 Arithmetic Unit arith ALU CIn Function(1:0) arithOut 0 0 A (default) A + B A + (not B) carry 01 10 ALUFunction arithOut 0 16 (15:0) VHDL entity 17 A+1 A +B+1 A-B [A+(not B)+1] A (default) 01 10 library IEEE: use IEEE. STD LOGIC 1164.ALL use IEEE.nuneric std.all: arithCln 1 entity arithUnit is : in std logic vector (15 downto 0) : in std_logic_vector (15 downto 0) port (A arithCIn: in std logic; ALUFunction: in std logic vector (1 dowmto 0) Component symbol : out std_logic : out std logic_vector (15 downto 0) arithout end entity arithUnit

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts