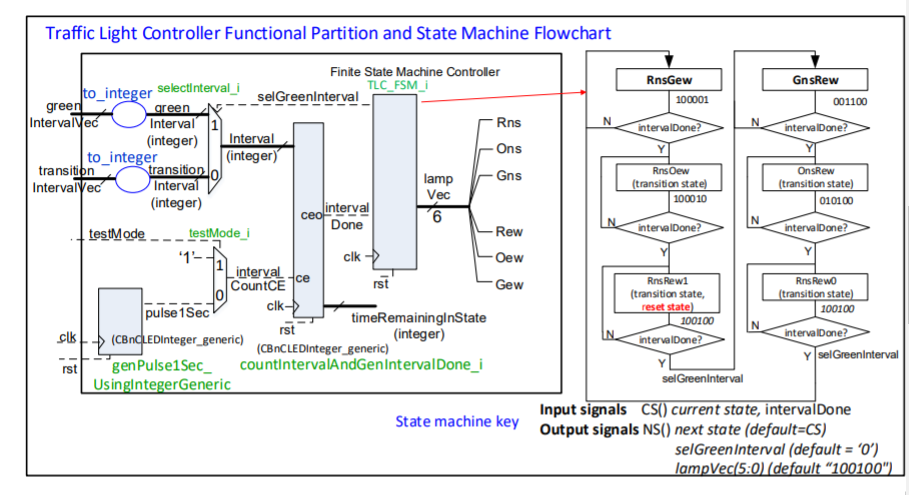

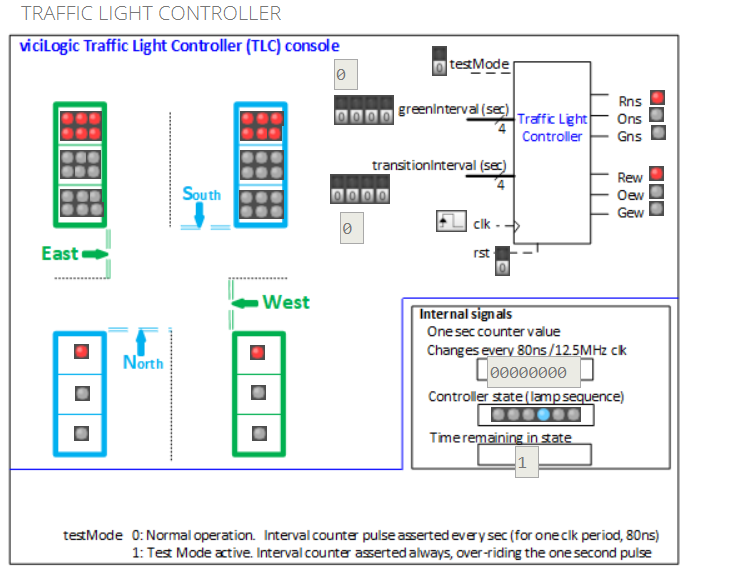

Question: VHDL- TRAFFIC LIGHT CONTROLLER Tasks Design the TLC digital system Include a Finite State Machine (FSM) controller instead of 80ns its 40ns and 25MHz clk

VHDL- TRAFFIC LIGHT CONTROLLER

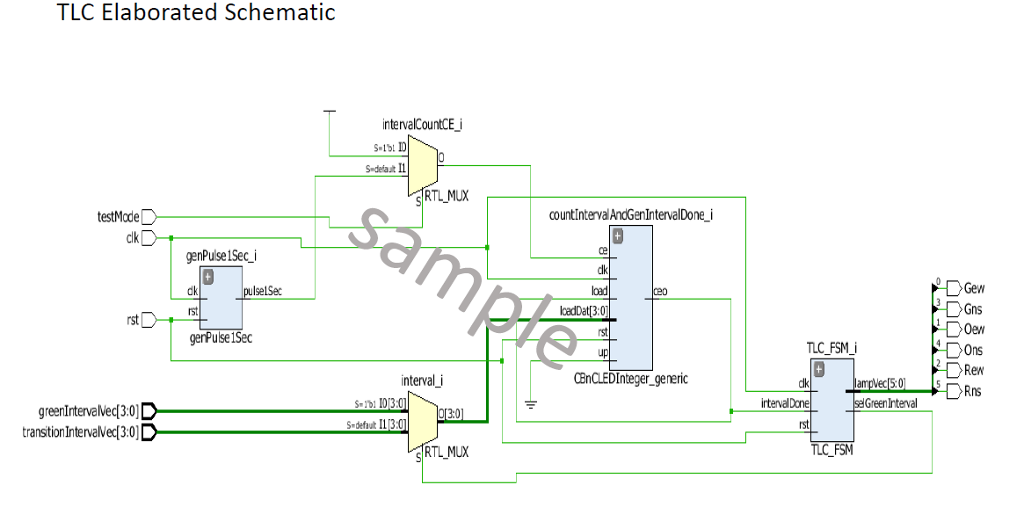

Tasks Design the TLC digital system Include a Finite State Machine (FSM) controller

![15 6 Lend TLC FSM; L7 18 E] architecture RTL of TLC](https://dsd5zvtm8ll6.cloudfront.net/si.experts.images/questions/2024/09/66f3db8837ae3_47966f3db87eed01.jpg)

instead of 80ns its 40ns and 25MHz clk

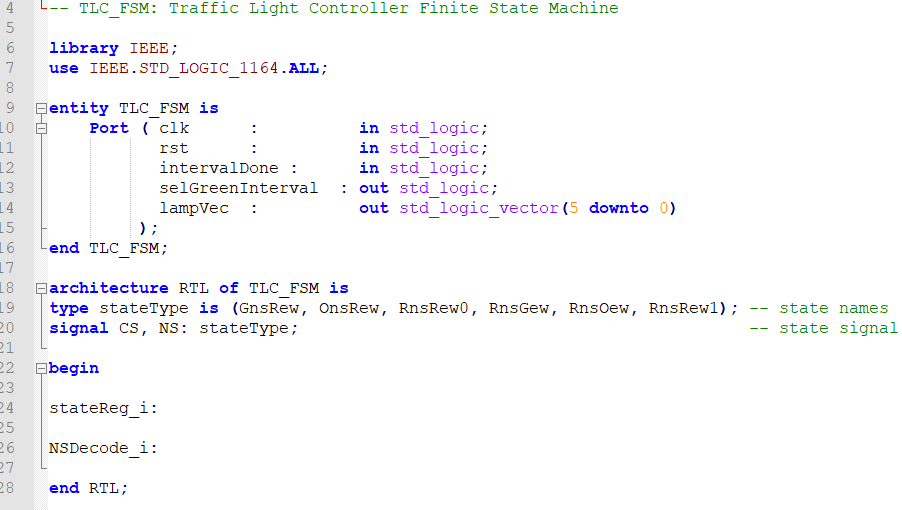

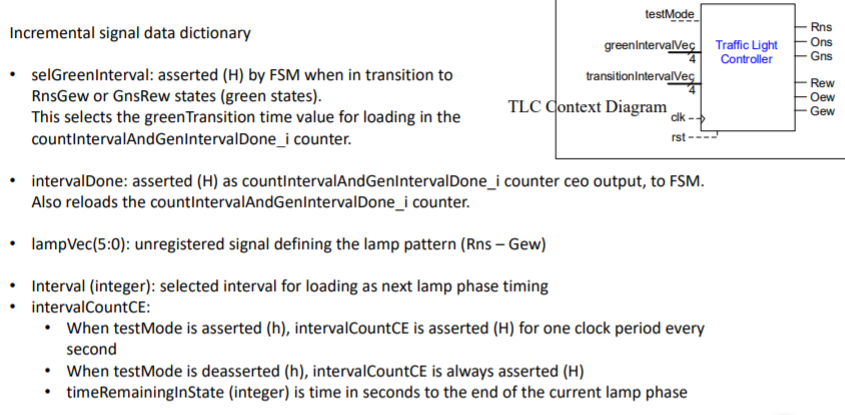

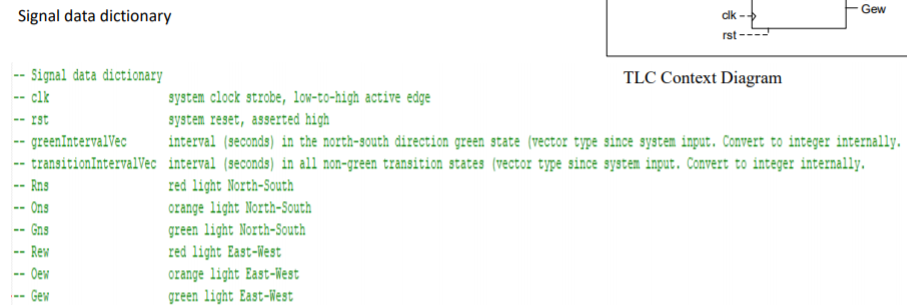

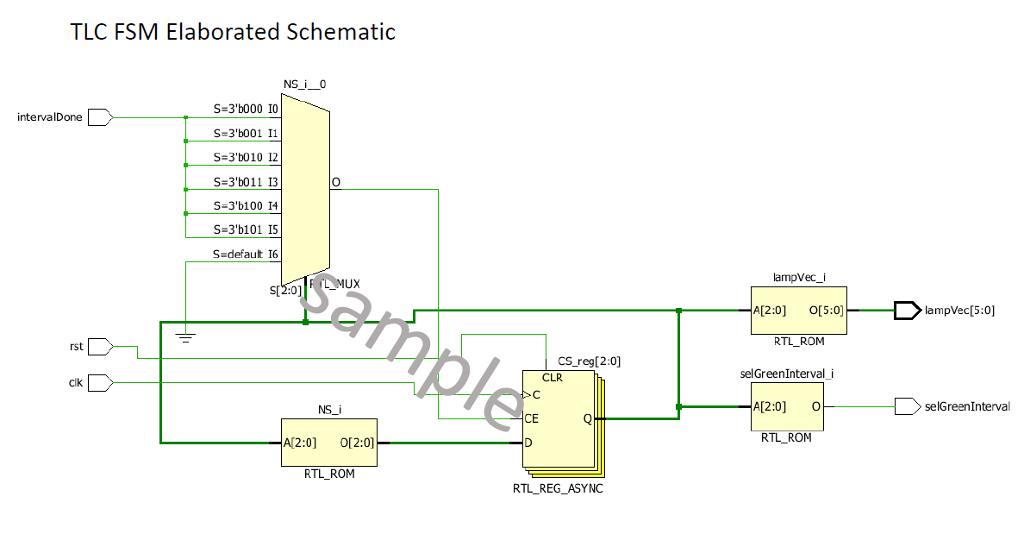

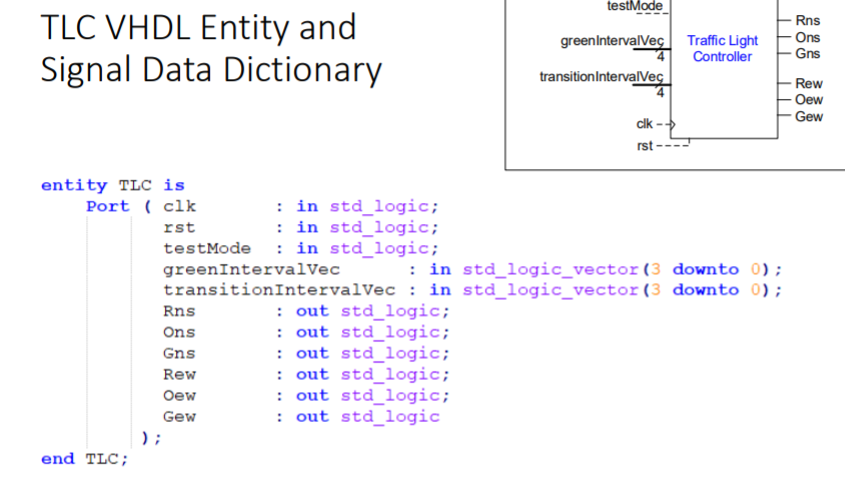

4 TLC FSM: Traffic Light Controller Finite State Machine 6 library IEEE; 7 use IEEE. STD LOGIC 1164.ALL; 9 L0 entity TLC FSM is Port ( clk in std logic; in std logic; in std logic; rst intervalDone: selGreenInterval : out std_logic; lampVec: L2 13 1 4 15 6 Lend TLC FSM; L7 18 E] architecture RTL of TLC FSM is 9 type stateType is (GnsRew, onsRew, RnsRew0, RnsGew, RnsOew, RnsRewl); state names 0 signal CS, NS: stateType; out std_logic_vector (5 downto 0) -- state signal begin 4 stateReg_i: 7 8 end RTL; 4 TLC FSM: Traffic Light Controller Finite State Machine 6 library IEEE; 7 use IEEE. STD LOGIC 1164.ALL; 9 L0 entity TLC FSM is Port ( clk in std logic; in std logic; in std logic; rst intervalDone: selGreenInterval : out std_logic; lampVec: L2 13 1 4 15 6 Lend TLC FSM; L7 18 E] architecture RTL of TLC FSM is 9 type stateType is (GnsRew, onsRew, RnsRew0, RnsGew, RnsOew, RnsRewl); state names 0 signal CS, NS: stateType; out std_logic_vector (5 downto 0) -- state signal begin 4 stateReg_i: 7 8 end RTL

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts